Устройство для селекции кодовзсесоюзнаяilaahthd'texhiisecha библиотека

Иллюстрации

Показать всеРеферат

О П И C А Н И Е 362292

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Ресотслик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 24.VII.1970 (№ 1470370/18-24) с присоединением заявки №

Приоритет

Л!. Кл. G 0613/04

Н 03k 19 00

Комитет по делам наобретений и открытий ори Совете Министров

СССР

УДК 681.32:31(088.8) Опубликовано 13.XII.1972, Бюллетень ¹ 2 за 1973 г.

Дата опубликования описания 25.1.1973

Автор изобретения

Л. В. Максимов

Заявитель

ВСеСОЮЗНАЯ

1 а Щ j 11,"ЩЩКЯ

БИБЛИОТЕКА

УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ КОДОВ

Изобретение относится к области вычислительной техники и может быть использовано для предварительной обработки дискретной информации и связи с цифровой вычислительной машиной.

Известны устройства для селекции кодов.

Известные устройства не обладают способностью выделять оперативную выборочную информацию из всего информационного потока, поступающего на их входы, поэтому с помощью таких устройств невозможно уплотнить поток оперативной информации, тем самым увеличить количество одновременно обслуживаемых линий связи.

Цель изобретения состоит в том, чтобы уплотнить выборочные взаимно несинхронизированные потоки информации.

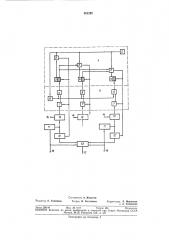

Сущность изобретения заключается в том, что устройство для селекции кодов содержит блоки программ, первые входы которых подключены к выходам одноименных узлов ввода кодов, а вторые входы соединены с шиной ввода программ, выход каждого блока программ через блок фазирования соединен с соответствующим входом блока анализа приоритета, каждый выход которого соединен со входом одноименного узла считывания кодов.

На чертеже представлена схема устройства для селекции кодов.

Она содержит блок анализа приоритета 1, в состав которого входит генератор импульсов

2, триггеры 8, 4, ..., и и схемы совпадения 5; блок фазирования б, включающий ячейки па5 мяти 7, формирователь импульсов 8 и схемы совпадения 9; блоки программ 10, узлы 11 ввода кодов, узлы 12 считывания кодов, выходной блок 18, шину 14 ввода программ, входы 15 и 1б и выход 17 устройства.

Блок программ 10 состоит из связанных между собой запоминающего устройства и устройства сравнения кодов. Запоминающее устройство подключено к одному из входов

15 устройства сравнения кодов. К другому входу этого устройства сравнения кодов подключен выход узла 11. Выход схемы сравнения (он же выход блока программ) связан с ячейкой памяти 7. В запоминающем устройстве блока

20 программ хранятся коды чисел, необходимые для выборки, и программа выборки этих кодов. Узел 11 представляет собой запоминающее устройство, где могут быть записаны числовые коды и признаки данной линии. Выхо25 ды узлов 12 подключены к выходу 17 через выходной блок 18. В этом блоке одноименные разряды числовых кодов от всех узлов 12 объединены и выведены на общую шину, Устройство для селекции кодов работает

30 следующим образом.

362292

3

В исходном состоянии сигнал на входах 15 и 16 отсутствует. В блоки программ 10 по шине 14 введена некоторая программа выборки кодов. Триггеры 8, 4,, и запрещают сигналы на выходах схем совпадения 5. Ячейки памяти 7 очищены и на их входы сигналы не поступают. Тактовые импульсы от генератора импульсов 2 динамического воздействия на элементы схемы не оказывают. На выходе

17 сигналы отсутствуют.

При работе устройства на входы 15 и 16 поступают коды чисел из несинхронизированных между собой линий связи. Эти коды фиксируются в узлах 11. Затем для каждой линии связи в отдельности происходит сравнение кодов чисел, находящихся в узлах 11, и кодов чисел, заданных в блоке программ 10. При совпадении кодов, устройство сравнения блока (п(ро(грамм (вырабаты(вает си(гнал ра(венева кодов. Этот сигнал поступает на вход ячейки памяти 7 и там запоминается.

Очередной тактовый импульс от генератора импульсов 2 своим передним фронтом, который выделен формирователем импульсов 8, переводит информацию, записанную во всех ячейках памяти 7, через схемы совпадения 9 в триггеры 8, 4, ..., и:.

:: Перевод информации из ячеек памяти в . триггеры параллельным кодом означает при " вязку по времени сигналов равенства кодов к фазе тактовых импульсов генератора. Опросными импульсами для всех ячеек памяти 7 является каждый тактовый импульс генератора. Параллельное фазирование сигналов равенства кодов устраняет зависимость периода поступления кодов на входы устройства от периода тактовых импульсов.

Код, записанный в триггерах 8, 4, ..., и, анализируется схемами совпадения 5 на предмет присвоения приоритета по важности обслуживаемой линии и по времени поступления кодов на входы устройства. Пусть, например, сигналы равенства кодов поступают одновременно на триггер 8 и триггер и. В этом случае триггеры 8 и и переключатся в состояние, отличное от исходного. Схема совпадения 5, подключенная к левому плечу триггера 8, подготавливается, а схемы совпадения, подключенные к правому плечу триггера 8, закрыты, поэтому тактовый импульс, переключающий триггеры 3 и и, проходит только через одну схему совпадения 5, в частности схему, подключенную к левому плечу тригге5

35 ра 8, с выхода которой импульс поступает на вход узла 12 и тем самым пропускает информацию из узла 11 в выходной блок 18. Задний фронт этого же тактового импульса устанавливает триггер 8 в исходное состояние и очищает ячейку памяти 7. Схема совпадения, подключенная в левое плечо триггера 3, переходит в исходное состояние, а схема совпадения, подключенная в левое плечо триггера и, подготавливается к работе.

Очередной второй тактовый импульс проходит через схему совпадения 5, подключенную к левому плечу триггера и. Остальные схемы находятся в исходном состоянии и не пропускают тактовые импульсы. На выходе 17 появляются сигналы кода выбранного числа, относящегося к и-му входу 16. Элементы схемы, относящиеся к и-му входу, задним фронтом второго тактового импульса приводятся в исходное состояние. Если в момент поступлени(я,второго тактового им(пульса (включается триггер 4, то подготавливается к работе схема совпадения, подключенная к левому плечу этого триггера, а все другие схемы совпадения

5 выключены.

Третий тактовый импульс обслуживает коды, поступающие по входу 16, однако этот вход не обслуживается, если с приходом третьего тактового импульса включается хотя бы один из триггеров с меньшим номером.

Таким образом, коды, поступающие через входы с меньшим порядковым номером, передаются на выход 17 в первую очередь и, следовательно, имеют приоритет перед кодами, поступившими через входы с большим порядковым номером.

Предмет изобретения

Устройство для селекции кодов, содержащее узлы ввода кодов, узлы считывания кодов, блок фазирования, блок анализа приоритета и выходной блок, отличающееся тем, что, с целью уплотнения выборочных взаимно несинхронизированных потоков информации, оно содержит блоки программ, первые входы кoTopbIx (под!ключены (K (Выходам (одноим(енных узлов ввода кодов, а вторые входы соединены с шиной ввода программ, выход каждого блока программ через блок фазирования соединен с соответствующим входом блока анализа приоритета, каждый выход которого соединен со входом одноименного узла считывания кодов.

362292

Редактор Е. Семанова

Заказ 200/16 Изд. № 1017 Тираж 404 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Составитель А. Жеренов

Техред Л. Богданова

Корректорьг Е Миронова и А. Степанова