Логический элемент

Иллюстрации

Показать всеРеферат

Со«сз Советских

Социалистических

Ресоублии

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 07.1Х.1970 (№ 1465381/18-24) с присоединением заявки №

Приоритет

М. Кл. Н 03k 19/00

Комитет оо лелем изобретений и открытий ори Совете Министров

СССР

Опубликовано 13.Х111972. Бюллетень № 2 за 1973

Дата опубликования описания 21.11.1973

УДК 681.325.65:621.382 (088.8) Авторы изобретения

Г. П. Липовецкий, П. В. Сивобород, В. И. Аствацатуров и В. В. Проценко

Заявитель

ЛОГИЧЕСКИИ ЭЛЕМЕНТ

Изобретение относится к радиотехническим устройствам.

Известны логические элементы на МДПтранзисторах.

Динамические логические элементы на

МДП-транзисторах отличаются высоким obIcTродействием, однако при создании различных устройств на их основе возникают значительные трудности, обусловленные сложностью передачи сигналов с одного элемента на другой, а также ограничениями по строгому согласованию во времени информационных сигналов.

Потенциальные элементы отличаются сравнительно высокой информационной надежностью и помехоустойчивостью при низком и среднем быстродействии и повышенной мощности потребления.

Применение в устройствах логических элементов обоих классов связано с дополнительными трудностями временного согласования.

Известна триггерная схема, сочетающая в себе преимущества потенциальных и динамических элементов на МДП-транзисторах, обладающая неограниченно низкой частотой следования тактовых импульсов, потенциальным выходом и высоким быстродействием.

Однако эта схема может выполнять только функцию элемента памяти и не позволяет использовать все преимущества подобных схем без схем, выполняющих логические функции.

Целью изобретения является создание логического элемента на МДП-транзисторах, реализующего функцию АВ и сочетающего в себе преимущества потенциальных и динамических элементов на МДП-транзистора i.

Для достижения цели в устройство дополнительно введен инвертор, напряжение с которого подается на дополнительно введенный транзистор, подключенный параллельно ключевому транзистору второго каскада триггера.

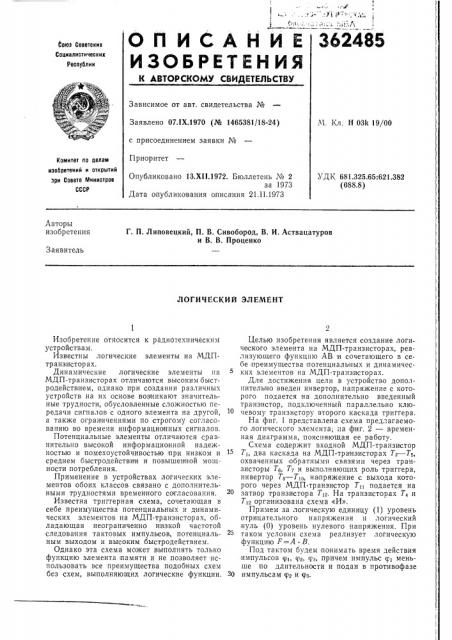

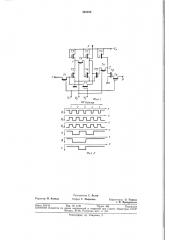

На фиг. 1 представлена схема предлагаемого логического элемента;,а фиг. 2 — временная диаграмма, поясняющая ее работу.

Схема содержит входной МДП-транзистор

Т,, два каскада на МДП-транзисторах Т вЂ” Те, охваченных обратными связями через транзисторы Т6, Тт и выполняющих роль триггера, инвертор T8 — T», напряжение с выхода которого через МДП-транзистор Т» подается на затвор транзистора Tä. На транзисторах Т„и

Т«г организована схема «И».

Примем за логическую единицу (1) уровень отрицательного напряжения и логический нуль (О) уровень нулевого напряжения. При таком условии схема реализует логическую функцию F=A В.

Под тактом будем понимать время действия импульсов «рт, «р, q», причем импульс «г меньше по длительности и подан в противофазе

30 импульсам «р и «рз.

362485

В № такта

2 .3

35

Предположим, что в исходном состоянии напряжение на выходе схемы равно нулю, т. е.

UF — — О. Напряжения на входах А и В также равны нулю, т. е. UA = О, Ув = О.

При подаче тактовых импульсов (1-й такт) импульсы cpz, q3 отключают обратные связи триггера посредством запирания транзисторов

Тб и Т, а также выход и нвертора от входа транзистора Тд путем запирания транзистора Т!!.

Состояние трипгера сохраняется за счет заряда емкостей затвор — подложка ключевых транзисторов Т и Т4.

После отключения обратных связей импульс ср! открывает транзисторы Т, и Т8. Входные напряжения UA и U> передаются на вход транзисторов Т и Та. Поскольку в рассматриваемом случае UA=0 =Î, то состояние транзисторов Т! и Та не изменится т. е. они будут заперты и напряжение в точках 1 и 2 будет отрицательным. По окончании также открываются транзисторы Т6 и Т!! и отрицательное напряжение с точек 1 и 2 передается на затворы транзисторов Т4 и Тд, которые откроются и подтвердят состояние Uz — — О.

Транзистор Т также открывается по концу, подтверждая состояние UF = О.

Из рассмотренного видно, что UF, будет равно единице в единственном случае, когда па затворы транзисторов Т и Т! будет подано нулевое напряжение.

Это, в свою очередь, соответствует случаю кода А =1 и В=1.

Рассмотрим этот случай (2-й) такт).

После отключения обратных связей импульс !

1 открывает транзисторы Т, и Т8. Отрицательные входные напряжения UA и U!!, через открытые транзисторы Т! и Т,, отпирают транзисторы Т и Т. Напряжение в точках 1 и 2 становится равным нулю. По концу такта напряжение точек 1 и 2 через открытые транзисторы Та и Т,! передается на затворы транзисторов Т! и Т!, которые запираются. Напряжение на выходе F с тTа нHоoвBи тTс я H р а вBнHbы!м 11, т. е.

UF=1, и через открытый транзистор Т7 поступает на вход транзистора Т, подтверждая состояние UF=1.

При других комбинациях входных напряжеНИй UA И Ув ПрОцЕСС рабОтЫ СХЕМЫ аиаЛОгичный.

Логическая операция выполняется во время действия тактовых импульсов, что способствует повышению быстродействия. С другой стороны, результат логической операции запоминается на триггере и может храниться при отсутствии тактовых импульсов, т. е. обладает потенциальным выходом, что является преимуществом предлагаемого логического элемента перед динамическими элементами.

Ниже приведена таблица истинности, в которой указан соответствующий такт на временной диаграмме, по концу которого выпо Iняется логическая операция, При необходимости выходной сигнал Ur может быть проинвертирован (U>) обычным инвертором, на вход которого подается сигнал

UF. В этом случае элемент реализует функцию АВ, Логический элемент на МДП-транзисторах реализуется в виде полупроводниковой интегральной микросхемы с использованием МДПтехнологии.

Предмет изобретения

Логический элемент, содержащий запоминающий элемент, выполненный в виде тритге4О ра на МДП-транзисторах по двухкаскадной схеме, охваченной управляемыми обратными связями, и ключевые МДП-транзисторы, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены до45 полнительный МДП-транзистор и инвертор на МДП-транзисторах,,причем затвор дополнительного транзистора подключен через ключевой МДП-транзистор к выходу инвертора, вход которого через другой ключевой МДПтранзистор соединен с одним из входов логического элемента.

362485

4 иг 2

Редактор Н. Коляда

Заказ 316/!4 Изд. № 1130 Тираж 404 Подписное

11HHHI1H Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 2 3 Ф ир 7

A = талта

2 д 4

Составитель С. Белан

Техред Т. Миронова

Корректоры: О. Тюрина и Н. Прокуратова