Реверсивный счетчик

Иллюстрации

Показать всеРеферат

О П И С-4ЫН-=И:Е

ИЗОБРЕТЕНИЯ

362490

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 22.Ч!.1970 (№ 1450885/18-24) с присоединением заявки №

Приоритет

М. Кл. Н 03k 23/00

Комитет по лелем наобретений и открытий при Совете Министров

СССР

УДК 681.325.5(088.8) Опубликовано 1,3.Х11.1972. Бюллетень № 2 за 1973

Дата опубликования описания 9.II.1973

Авторы изобретения

Заявитель

В. И. Корнейчук и В. П. Тарасенко

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции

РЕВЕРСИ ВНЫЙ СЧЕТЧИ К

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных и измерительных устройствах.

Известен реверсивный счетчик на основе десятичного регистра, который содержит десятичный регистр на фазоимпульсных многоустойчивых элементах, десятичный фазоимпульсный сумматор, коммутатор разрядов, генератор констант, генератор тактовых импульсов, синхронизатор, триггеры и логические элементы.

Однако быстродействие известного счетчика относительно невысоко, так как его скорость счета импульсов составляет илттт/сек, где

20п

t — частота 1актовых импульсов; n — количество десятичных разрядов в регистре.

Целью изобретения является повышение быстродействия счетчика.

Поставленная цель достигается тем, что в счетчик дополнительно введены схемы «И» и управляющий автомат, причем выход суммы сумматора через первую схему «И», второй вход которой соединен с первым выходом управляющего автомата, подсоединен ко входу регистра и ко второй и третьей схемам «И», вторые входы которых соединены с единичным и нулевым вы одами триггера, нулевой вход которого подключен к выходу переноса сумматора, причем выход второй схемы «И» соединен со входом установки в исходное положение коммутатора разрядов и со вторым

5 входом управляющего автомата, а выход третьей схемы «И» соединен с единичным входом триггера, со входом сдвига коммутатора разрядов и через схему «ИЛИ», второй вход которой подсоединен ко входной клемме счет10 чика, с первым входом управляющего автомата, третий вход которого соединен со входом сумматора и с выходом четвертой схемы «И», входы которой подключены к выходу регистра и ко второму выходу управляющего ав15 томата. Входы сложения и вычитания сумматора соединены со входными клеммами.

Быстродействие описываемого ниже счетчиf

10п + 1

10п +9 ка определяется выражениями

20 и,на/сек в режиме сложения, иип/сек — в режиме вычитания.

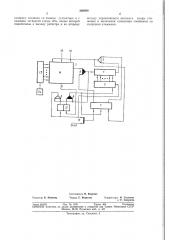

На чертеже изображена схема предлагаемо25 го реверсивного счетчика.

Счетчик состоит из десятичного фазоимпульсного регистра 1, управляемого коммутатором разрядов 2. Выход регистра соединен со входом схемы 3 типа «И», выход которой под30 веден ко входу десятичного фазоимпульсного

362490

35

60

65 сумматора 4. Выход 5 сумматора, соответствующий сигналам суммы (разности), подключен к схеме 6 типа «И», второй вход которой соединен с первым выходом управляющего автомата 7. Выход схемы 6 подведен ко входу регистра 1 и ко входам схем 8 и 9 типа «И».

Вторые входы схем 8 и 9 соединены соответственно с единичным и нулевым выходами триггера 10. 1 нулевому входу триггера 10 подключен выход 11 сумматора 4, соответствую.щий сигналам переноса (заема). Выход схемы

8 подведен ко второму входу управляющего автомата 7 и ко входу установки в исходное положение коммутатора разрядов 2. В свою очередь, выход схемы 9 подключен к единичному входу триггера 10, ко входу сдвига коммутатора разрядов 2 и ко входу схемы 12 типа «ИЛИ». Второй вход схемы 12 является входом счетчика, а ее выход подведен к первому входу управляющего автомата 7. Третий вход управляющего автомата связан с выходом схемы 8, а второй его выход подключен ко второму входу этой же схемы, Синхронная работа всех узлов счетчика обеспечивается генераторами 18 фазоимпульсных констант и 14 тактовых импульсов.

Управляющий автомат 7 может быть реализован, например, на двух триггерах.

Работа счетчика состоит в следующем.

Предположим, что в младшем разряде регистра 1 находится число Х. Входной импульс устанавливает управляющий автомат 7 в состояние «1». При этом на первом выходе автомата 7 появляется нулевой сигнал, а на втором — единичный сигнал, открывающий схему

8. Тогда импульс, соответствующий числу Х (импульс Х), с выхода регистра 1 проходит через схему 8 и поступает на сумматор 4 и автомат 7, устанавливая последний в состояние «2» и, тем самым, открывая схему б и закрывая схему 8. В зависимости от режима работы счетчика, определяемого единичным сигналом по шинам 15 и 16 (15 — сложение, 16— вычитание), на выходе сумматора 4 появится импульс X+1 (mod 10), который проходит через схему б на вход регистра 1, так как автомат 7 находится в состоянии «2». Этот же импульс поступает на входы схем 8 и 9, которые управляются сигналами с выходов триггера 10. Если при обработке первого разряда регистра возник сигнал переноса (заема), то триггер 10 устанавливается этим сигналом в нулевое состояние, открывая схему 9. Поэтому импульс с выхода схемы 9 сдвинет коммутатор разрядов 2 на один разряд влево, установит триггер 10 в единичное состояние и автомат 7 — снова в состояние «1». Вследствие этого произойдет прибавление (вычитание) единицы к содержимому следующего разряда регистра. Если же сигнал переноса (заема) при обработке очередного разряда не возник, то будет открыта схема 8. Импульс с выхода схемы 8 установит коммутатор разрядов 2 в исходное положение, а автомат ? — в состояние «3», при котором на обоих выходах автомата появляются нулевые сигналы. С приходом следующего входного импульса описанный процесс повторяется.

В режиме сложения для занесения в младший разряд счетчика числа Х+1 (mod 10) требуется один такт, поскольку при фазоимпульсном представлении информации импульс

Х+1 (mod 10) следует сразу же за импульсом

Х. Если при обработке младшего разряда возникает перенос, то для его прибавления к содержимому следующего разряда необходимо повторное срабатывание коммутатора 2, сумматора 4 и управляющего автомата 7. Для этого требуется одиннадцать тактов. В случае, когда переносы могут появиться во всех и разрядах счетчика, время счета одного импульса будет равно 10 и+ 1 тактов.

В режиме вычитания для занесения в младший разряд счетчика числа Х вЂ” 1 (mod 10) требуется девять тактов, так как при фазоимпульсном представлении информации импульс

Х вЂ” 1 (mod 10) может появиться лишь через девять тактов после импульса Х. Если сигналы заема возникают при обработке всех и разрядов, то время вычитания одного импульса равно 10 n+9 тактов.

Следовательно, быстродействие описываемого счетчика составляет ими сек в pe10n + 1 жиме сложения и имгг/сек в режиме

10п + сг вычитания, где f — тактовая частота.

Предмет изобретения

Реверсивный счетчик, содержащий десятичный фазоимпульсный регистр, десятичный сумматор, коммутатор разрядов, генератор констант, генератор тактовых импульсов, схемы «И», «ИЛИ» и триггер, причем выход геператора тактовых импульсов связан со входом генератора констант, выходы которого соединены со входами сумматора, а выходы коммутатора разрядов связаны с десятичным регистром, отличающийся тем, что, с целью повышения быстродействия, в него дополнительно введены схемы «И» и управляющая схема, причем выход суммы сумматора через первую схему «И», второй вход которой соединен с первым выходом управляющего автомата, подсоединен ко входу регистра и ко второй и третьей схемам «И», вторые входы которых соединены с единичным и нулевым выходами триггера, нулевой вход которого подключен к выходу переноса сумматора, причем выход второй схемы «И» соединен со входом установки в исходное положение коммутатора разрядов и со вторым входом управляющего автомата, а выход третьей схемы «И» соединен с единичным входом триггера, со ,входом сдвига коммутатора разрядов и через схему «ИЛИ», второй вход которой подсоединен ко входной клемме счетчика, с первым входом управляющего автомата, третий вход

362490 выходу управляющего автомата, входы сложения и вычитания сумматора соединены со входными клеммами.

Составитель В. Бакулии

Техред Е. Борисова

Редактор Б. Нанкина

Заказ 244/l6 Изд. Мв 1035 Тираж 404 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 которого соединен со входом сумматора и с выходом четвертой схемы «И», входы которой подключены к выходу регистра и ко второму

Корректоры: Н. Стельмах и E. Сапунова