Система для обработки информации

Иллюстрации

Показать всеРеферат

ОПИСАHИЕ 363266

ИЗОБРЕТЕНИЯ

К ПАТЕНТУ

Ооеа Советских

Социалистических

Республик

Зависимый от патента №

М. Кл. С 06f 11/00

G 061 15/46

Заявлено 02.Х.1969 (№ 1364887/18-24)

Приоритет 28.Х.1968, ¹ 14530/68, Швеция

Комитет па делам изобретений н открытий при Совете Министров

СССР

Опубликовано 20.XII,1972. Бюллетень № 3 за 1973

УДК 681.326.3 (088.8) Дата опубликования описания 14.III.1973

Авторы изобретения

Иностранцы

Нильс Герберт Эдстрем (Швеция) и Геран Андерс Хенрик Хемдал (Финляндия) Иностранная фирма

«Телефон Актиеболагет Л. М, Эрикссон» (Швеция) Заявитель

СИСТЕМА ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ

Изооретение относится к системам для разгрузки от сканирования центрального блока вычислительных машин, управляющих процессо.м.

Известны устройства, в которых вычисли- 5 тельная машина производит циклическое сканирование контрольных точек, относящихся к данному процессу, в результате чего, если их состояния изменились, вычислительная машина выполняет определенные программы, вслед- 10 ствие которых осуществляется вмешательство машины в ход процессов при помощи функционального блока. Например, это относится к .системам телефонной связи, управляемым вычислительными машинами, в которых скани- 15 руются абонентные повторы и производится выполнение или разрыв определенных соединений при изменении состояния абонента. При этом необходимо, чтобы сканирования состояний абонента производились достаточно часто 20 для того, чтобы обнаружить каждое изменение состояния. Высокая частота сканирования при водит к тому, что в большинстве случаев сканирование указывает на отсутствие каких-либо изменений состояния, и поэтому централь- 25 ный блок будет занят несложной работой, заключающейся в сканировании процесса. Поэтому по крайней мере для конкретных контрольных точек сканирование следует выполнять прн помощи отдельных сканирующих устройств, от которых должна быть получена информация о наличии каких-либо изменений состояний в контрольных точках. В связи с этим необходимо передавать как адрес, так и состояние сканируемых контрольных точек с центрального блока на блок сканирования, чтобы обнаружить изменения состояния, поэтому требуется очень большая передающая емкость между центральным и сканирующим блоком, либо сканирующий блок должен быть полнообъемным запоминающим устройством для записи состояний и сравнения их с предыдущими состояниями. В последнем случае, кроме того, требуется, чтобы при записи изменения состояния, адрес слова в запоминающем устройстве вычислительной машины, в котором записывается состояние данной контрольной точки, вычислялся центральным блоком.

Цель изобретения — построение устройства, в котором центральный блок существенно разгружен от сканирования.

Предлагаемая система отличается от известных тем, что она содержит блоки памяти, индикатор, селектор, регистры с числом разрядов по числу датчиков в группе, логическую схему, дешифратор и схемы совпадения, причем вход каждого из блоков памяти соединен

363266

3 с соответствующим датчиком, а выходы блоков памяти через селектор соединены со входом триггера, выход которого через первую схему совпадения и дешифратор соединен со входом адресного регистра запоминающего устройства вычислительной машины, число разрядов которого соответствует числу групп датчиков,,выход триггера через вторую схему совпадения, присоединенную своим входом к выходу селектора, подключен к первому регистру. Выход последнего через логическую схему подключен ко входу второго регистра, а его выход соединен со входом запоминающего устройства вычислительной машины. Такое выполнение повышает быстродействие системы.

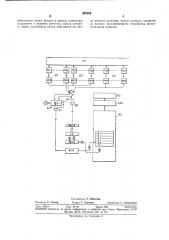

На чертеже изображена система для обработки информации. На ней позицией ТЕ обозначен объект, управляемый при помощи вычислительной машины, который может, например, представлять системы дальней связи.

Датчики Т«..... Т „, разделенные на группы G>, Gz..... G,, относятся к объекту, причем состояния указанных контрольных датчиков соответствуют состояниям различных частей этого объекта. В соответствии с настоящим изобретением, запоминающие устройства блоки памяти М«.... M >, относящиеся к каждому датчику, срабатывают в том случае, ксгда соответствующий датчик изменяет свое состояние. Накопительные устройства могут быть, например, выполнены на конденсаторах, полярность которых меняется на противоположную при изменении состояний. Кроме того, данное устройство содержит блок сканирования и индикации SCP, управляемый генератором синхроимпульсов К, переключающий искатель — селектор. В результате чего этот искатель последовательно подключается к группам накопительных устройств и информация о состоянии возбуждения устройств,в соответствующих группах поступает от искателя по нескольким проводникам. На чертеже эти проводники условно изображены одной линией, идущей от искателя. Выходные сигналы искателя подаются на триггер Т схемы сканирования через схему «ИЛИ» (на чертеже не показана), в результате чего триггер устанавливается в единоличное состояние, если какое-либо из запоминающих устройств в сканированной группе возбуждено. Единичное состояние триггера открывает две схемы совпадения 01 и 02, соответствующим образом соединенные с триггером. По упомянутым параллельным проводникам, идущим от искателя, сигналы со сканированных запоминающих устройств подаются через схему совпадения 02 (на самом деле состоящую из нескольких параллельных схем) на регистр PEGA, который имеет несколько цифровых разрядов, соответствующих числу запоминающих устройств в каждой группе. В результате цифровые разряды регистра, соответствующие возбужденным устройствам, устанавливаются в единицу. С устройства сканирования 3СР информация о положении искателя через схему 01 подается на дешифратор АVK. В дешифраторе г:ринятая информация переводится по адресу

В 1 в запоминающее устройство DS вычислительной машины, где накапливаются те состояния датчиков, запоминающие устройства которых были сканированы. Затем этот адрес посылается дешифратором (см. стрелку А).

В результате такой посылки маркерный бит

ЛИ, соответствующий данному адресу, устанавливается в единичное состояние, а слово, помещенное по этому адресу, считывается на регистр REGB (стрелка В). Регистры РЕ6Л и КЕGB соединены с логической схемой LC, выходной сигнал которой подается на регистр

ДЕЙВ. Логическая схема устроена таким образом, что на десятичных разрядах, установленных в единицу в регистре REGS, десятичная информация в регистре REGB имеет противоположный знак, т. е. единицы инвертированы в нули и наоборот. При этом десятичные .разряды регистра РЕЙВ, соответствующие датчикам, в которых произошло изменение состояния, инвертируются (см. стрелки Си D).

Слово, полученное таким путем в регистре

Г<ЕОВ, будет после этого записано по своему гервопачальному адресу ВА в запоминающее устройство В5 (стрелка E). Теперь центральный блок СРО вычислительной машины опрашивает запоминающее устройство DS при помощи команд из программного накопительного устройства PS. Однако, это необходимо только для того, чтобы тщательно проверить содержимое тех адресов, маркерные биты которых установлены в единицу, и выявить состояние каких контрольных точек изменилось, в результате этого достигается значительная разгрузка центрального блока.

На чертеже показан только один блок сканирования, однако дешифратор может обслужить несколько таких блоков при условии, что на входе дешифратора будут установлены буферные регистры.

Предмет изобретения

Система для обработки информации, содержащая датчики, разделенные на группы, и вычислительную машину, отличающаяся тем, что, с целью повышения быстродействия, она содержит блоки памяти, триггер, селектор, регистры с числом разрядов по количеству контрольных датчиков в группе, логическую схему, дешифратор и схемы совпадения, причем вход каждого из блоков памяти соединен с соответствующим контрольным датчиком, а выходы блоков памяти через селектор соединены со входом триггера, выход которого через первую схему совпадения и дешифратор соединен со входом адресного регистра вычислительной машины, число разрядов которого соответствует числу групп датчиков, выход триггера через вторую схему совпадения, подМ8266

Составитель Е. Иванеева

Техред Т. Курилко

Редактор Е. Гончар

Корректор С. Сатагулова

Заказ 268/15 Изд. № 60 Тираж 404 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, )К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 включенную своим, входом к выходу селектора, подключен к первому регистру, выход которого через логическую схему подключен ко входу второго регистра, выход которого соединен сп входом запоминающего устройства вычислительной машины.