Устройство для вычисления разности фаз сигналов с относительной фазовой манипуляцией

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

363986

Вова Соеетаимв

Социалистичесыиз

Республик

Зависимое от авт. свидетельства №

М. Кл, G 06g 7/14

Н 03k 7104

Заявлено 29111.1971 (№ 1642224126-9) с присоединением заявки №

Комитет ао делам иаобретеиий и открытий при Совете Министров

СССР

Приоритет

УДК 621.376.52(088.8) Опубликовано 25.XII.1972. Бюллетень ¹ 4 за 1973

Дата опубликования описания 21.П.1973

Авторы изобретения

А. Ю. Лев и Л. М. Рахович

Одесский электротехнический институт связи им. А. С. Попова

Заявитель

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ РАЗНОСТИ ФАЗ

СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ

Изобретение относится к области техники связи.

Известно устройство для вычисления разности фаз сигналов с относительной фазовой манипуляцией, содержащее последовательно соединенные аналоговый инвертор и управляемый ключ, параллельно которым подключен второй управляемый ключ, интегратор, источник пилообразного напряжения, подключенный ко входу схемы сравнения, и вход предыдущей посылки.

Цель изобретения — повышение точности вычисления.

Поставленная цель достигается тем, что вход предыдущей посылки подключен ко второму входу схемы сравнения, выход которой через схему совпадения подключен к управляющему входу первого ключа, а через логический инвертор и вторую схему совпадения — к управляющему входу второго ключа, выход источника пилообразного напряжения через дополнительную схему сравнения подключен ко второму входу второй схемы совпадения и через второй логический инвертор — ко второму входу первой схемы совпадения, причем второй вход дополнительной схемы сравнения соединен с корпусом.

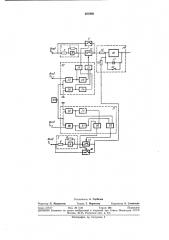

На чертеже изображена функциональная блок-схема устройства.

Устройство имеет четыре входа и один выход. Входные клеммы устройства соединены с элементами памяти приемника, в которых хранятся напряжения, соответствующие проекциям сигнала очередной (Х„и Y ) и предыдущей (Х 1 и Y> <) посылок.

Входные клеммы устройства, на которые подаются проекции сигнала очередной посылки, присоединены ко входам двух инверторов

10 1 и 2, состоящих из усилителей 8 и 4 постоянного тока и двух пар резисторов 5, 7 и 6, 8 и ко входам двух ключей 9 и 10, например, на транзисторах. Выходы инверторов 1 и 2 присоединены ко входам ключей 11 и 12. Выхо1S ды ключей 9 и 11 присоединены к резистору

18 интегратора 14, а выходы ключей 10 и

12 — к резистору 15 того же интегратора.

Интегратор представляет собой операционный усилитель 16, например, на основе ин20 тегральной микросхемы, с конденсатором 17, включенным между входом и выходом усилителя. Параллельно конденсатору присоединен ключ 18 сброса (разряда конденсатора).

Управляющие входы ключей 9 и 10 присо25 единены к выходам схем 19 и 20 совпадения, а ключей 11 и 12 — к выходам схем 21 и 22 совпадения. Схемы 19 — 22 совпадения представляют собой, например, интегральные микросхемы.

363986

Входы схемы 19 совпадения присоединены к выходу ехемы 28 сравнения, представляющей собой, например, операционный усилитель, и к выходу логического инвертора 24, например, на транзисторе, а входы схемы 21 совпадения — к выходу схемы 25 сравнения и к выходу логического инвертора 26. Входы логических инверторов 24 и 2б присоединены к выходам схем 28 и 25 сравнения соответственно. Соединения схем 20 и 22 совпадения соединены логическими инверторами 27 и 28 и со схемами 29 и 80 совпадения блока 81, задающего интервал интегрирования, выполнены аналогично соединениям в блоке 82.

Выход генератора 88 пилообразного напряжения подключен к инвертирующим входам схем 28, 25, 29 и 80. Неинвертирующие входы схем 28 и 29 присоединены к входным клеммам устройства, заведенным на выходы элементов памяти приемника, хранящих проекции сигнала предыдущей посылки Х„ и Yn-i соответственно. Неинвертирующие входы схем 25 и 80 заземлены.

Определение значения косинуса разности фаз предыдущеи и очередной посылок сигнала (сов ф) производится согласно алгоритму сos g: Yn — » Y»»+Х Х вЂ” »

Величины произведений Х» Х и» » У »- вычисляются, как и в прототипе, путем интегрирования величины >и (или An) в течение времени, пропорционального (У», <) или (»» — 1) .

1 ля формирования интервала интегрирования„пропорционального, например, Х» < и устаноаки знака A„, используется генератор .пилоооразного напряжения, две схемы 28 и ыо сравнения, два логических инвертора 24 и 4ä и две схемы l9 и 21 совпадения. Размах значений напряжения генератора пилоооразного (растущего) напряжения перекрывает размах значений Х», .

1!окажем, что при положительном Х» замыкается ключ 9, на время, пропорциональное аосолютной величине Л»» ь

Для этого необходимо, чтобы на обеих входах схемы 19 совпадения появился положительный потенциал. Положительный потенциал на выходе логического инвертора 24 наблюдается при положительном пилообразном напряжении, положительный потенциал на выходе схемы 28 сравнения — то время, ког5

50 да пилообразное напряжение отрицательное (меньше) Х <. Таким образом, совпадение положительных потенциалов на входах схемы 19 совпадения наблюдается в течение интсрвала времени, когда пилообразное напряжение изменяется, от нуля до величины, равной Х . Очевидно этот интервал пропорционален абсолютной величине Х,, Аналогично можно показать, что ключ 11 при положительном Х„» закрыт и на вход интегратора 14 поступает только неинвертированное значение А>.

При отрицательном Х„ совпадение положительных потенциалов происходит на входах схемы 21 совпадения, замыкается только ключ 11 и на вход интегратора 14 поступает инвертированное значение Х»,. Интегрирование начинается, когда пилообразное напряжение превышает Х„» и заканчивается, когда пилообразное напряжение становится оольше нуля. Интервал интегрирования будет также пропорциональным (An z).

Формирование интервала, пропорционального абсолютной величине» » ь и выбор инвертированного или неинвертированного значения Y ïðîèçâîäÿòñÿ аналогично.

Предмет изобретения

Устройство для вычисления разности фаз сигналов с относительной фазовой манипуляцией, содержащее последовательно соединенные аналоговый инвертор и управляемый ключ, параллельно которым подключен второй управляемый ключ, интегратор, источник пилоооразного напряжения, подключенный ко входу схемы сравнения, и вход предыдущей посылки, отличающееся тем, что, с целью повышения точности вычисления, вход предыдущей посылки подключен ко второму входу схемы сравнения, выход которой через схему совпадения подключен к управляющему входу первого ключа, а через логический инвертор и вторую схему совпадения — к управляющему входу второго ключа, выход источника пилообразного напряжения через дополнительную схему сравнения подключен ко второму входу второй схемы совпадения и через второй логический инвертор — ко второму входу первой схемы совпадения, причем второй вход дополнительной схемы сравнения соединен с корпусом.

363Я86

Корректор А. Степанова

Редактор Л. Мазуронок

Заказ 317/17 Изд. № 1129 Тираж 404 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Вк л

Составитель А. Горбачев

Техред Т. Миронова