Устройство для оценки качества сигнала

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

364И7

Социалистических

Республик

За висимое от авт. свидетельства ¹â€”

Заявлено 20.V111.1969 (№ 1357281/26-9) с присоединением заявки ¹â€”

Приоритет—

Опубликовано 25.XII.1972. Бюллетень № 4 за 1973

Дата опубликования описания 12.111.1973

М..Кл. Н 041 1 10

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 621.391.833.44 (088.8) Авторы изо бретения

Г. И. Прохоров, В. А. Ржавин и Ю. К. Шляхов

Заявитель

УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА СИГНАЛА

Известны устройства для оценки качества сигнала в каналах цифровой связи, содержащие накопитель когда на и периодов сообще. ния и (и+1) маркеров, соединенный с (и+1) дешифраторами маркеров и анализатором качества сигнала, на который поданы сигналы групповой фазы, и счетчик по модулю У, ко входу которого подключена шина тактовых импульсов, а выход которого через схему «НЕТ» соединен со входом «Запрет анализа» анализатора качества сигнала.

Цель изобретения — повышение достоверности оценки качества принимаемого сигнала.

Это достигается тем, что выход первого дешифратора маркера подключен к двухвходовой схеме совпадения и к (n+I) трехвходовым схемам совпадения, выход второго дешифратора маркера подключен к схеме «ИЛИ», ко второму входу двухвходовой схемы совпадения и к каждой из (и — 1) решающих схем, выходы которых подключены ко вторым входам cootветствующих трехвходовых схем совпадения, выход каждого последующего дешифратора маркера, начиная с третьего, подключен к соответствующей решающей схеме, начиная со второй, и ко всем последующим, а также к третьему входу соответствующей трехвходовой схемы совпадения и к схеме «ИЛИ», выход которой подсоединен к запрещающему входу схемы «НЕТ».

При этом выход каждой из схем совпадения через вторую схему «ИЛИ» соединен со входом «Сброс» счетчика по модулю N и входом «Разрешение анализа» анализатора качества сигнала.

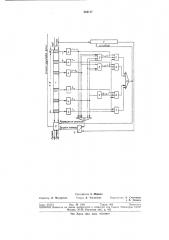

На чертеже приведена блок-схема устройства, где:

1 — накопитель кода на и периодов сообщения и (и+1) маркеров;

2 — анализатор качества сигнала;

8 — счетчик по модулю Х; 1 — дешифратор маркеров;

5 — решающая схема; б — трехвходовая схема совпадения; !

5 7 — двухвходовая схема совпадения;

8 — схема «ИЛИ»;

9 — схема «НЕТ»;

10 — схема «ИЛИ».

Входными сигналами устройства являются код, такты регенератора и сигнал групповой фазы, поступаю!цпй от синхронизатора.

В процессе приема символы кода проходят через накопите.-» кода 1 и поступают на апа,!!!затор ачества сиг!!ала 2. Счетчик по модулю Л 3 осуществляет счет количества поступивших символов по модулю Л, каждый из (n+ I ) дешифраторов маркеров 4 формирует на выходе сигнал при поступлении на его вход т„.-разрядного маркера структуры, а кажЗ0 дая из,решающих схем 5 регистрирует поступ364117 ление на ее вход периодических маркеров в количестве, не меньшем установленного критерием периодичности.

При одновременном наличии сигнала на выходе 1„и каких либо других выходах дешифраторов маркеров 4 с выходов соответствующих решающих схем 5 на трех входовые схемы совпадения 6 поступают сигналы, которые совместно с сигналами дешифраторов маркеров 4 о наличии маркеров на границах отрезков формируют на выходах соответствующих трехвходовых схем совпадения б сигналы об обнаружении отрезка, периодичность структу ры которого удовлетворяет установленному для отрезка данной длины критерию периодичности. Например, для отрезка длиной и периодов сигнал на выходе трехвходовой схемы совпадения б появляется при наличии си.палов с выходов 1„и (и+1) „дешифраторов маркеров 4 и наличии не менее k из (n — 1) сигналов на входе решающей схемы 5, а для отрезка длиной (и — 1) периодов — при наличии сигналов с выходов 1„и и„дешифраторов маркеров 4 и не менее i из (n — 2) сигналов на входе решающей схемы 5. При наличии сигналов маркеров только на выходах 1„и 2„ дешифраторов маркеров 4 сигнал об обнаружении отрезка с периодической структурой формируется двухвходовой схемой совпадения 7.

Сигналы с выходов двухвходовой схемы совпадения 7 и трехвходовой схемы совпадения 6 через схему «ИЛИ» 8 поступают на анализатор качества сигнала 2, разрешая производить оценку качества сигнала по критерию декодируемости знаков, границы которых определяются сигналами групповой фазы синхронизатора, и, в зависимости от результатов этой оценки, формировать команды «Сигнал» или «Помеха». Кроме того, сигнал с выхода схемы «ИЛИ» 8 поступает на установку исходного состояния счетчика по модулю Л 3, благодаря чему последний начинает вести счет количества тактов, необходимых для вывода всего обнаруженного отрезка с периодической структурой из накопителя кода 1.

Сигнал с выхода счетчика по модулю ЖЗ, появляющийся при отсчете очередных N тактов, поступает на вход схемы «НЕТ» 9, вход запрещения которой через схему «ИЛИ» 16 соединен с выходами 2„, 3„, ...и„(и+1)и дсшифраторов маркеров 4, благодаря чему схема «НЕТ» 9 не вырабатывает сигнала «3апрет анализа» до тех пор, пока из накопителя кода 1 не будет выведен последний период обнаруженного отрезка с периодической структурой.

При отсутствии сигнала на входе запрещения схемы «НЕТ» 9 и поступлении очередного сигнала с выхода счетчика по модулю Л 3 схема «НЕТ» 9 формирует сигнал «Запрет анализа», по которому анализатор качества сигнала 2 будет вырабатывать команду «Помеха» до обнаружения следующего отрезка сообщения, удовлетворяющего критерию сохранения периода следования маркеров структуры и критерию декодируемости.

Предмет изобретения

Устройство для оценки качества сигнала в каналах цифровой связи, содержащее накопитель кода на и периодов сообщения и (и+1) маркеров, соединенный с (и+1) дешифраторами маркеров и анализатором качества сигнала, на который поданы сигналы групповой фазы, и счетчик по модулю N, ко входу которого подключена шина тактовых импульсов, а выход которого через схему «НЕТ» соединен со входом «Запрет анализа» анализатора

ЗО качества сигнала, отличающееся тем, что, с целью повышения достоверности оценки качества принимаемого сигнала, выход первого дешифратора маркера подключен к двухвходовой схеме совпадения и к (и+1) трехвходо35 вым схемам совпадения, выход второго дешифратора маркера подключен к схеме

«ИЛИ», ко второму входу двухвходовой схемы совпадения и к каждой из (n — 1) решающих схем, выходы которых г.одключены ко вторым

40 входам соответствующих трехвходовых схем совпадения, выход каждого последующего,дешифратора маркера, начиная с третьего, подключен к соответствующей решающей схеме. начиная со второй, и ко всем последующим, 45 а также к третьему входу соответствующей трехвходовой схемы совпадения и к схеме

«ИЛИ», выход которой подсоединен к запрещающему .входу схемы «НЕТ», причем выход каждой из схем совпадения через вторую схему «ИЛИ» соединен со входом «Сброс» счетчика по модулю N и входом «Разрешение анализа» анализатора качества сигнала.

Составитель А. Мермаи

Редактор Л. Мазуронок Тсхред Л. Богданова Корректоры А. Степанова и Е. Энмииа

Заказ 27/271 Изд. № 1058 Тираж 404 Подписное

ЦНИИПИ Комит та по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»