Функциональный преобразователь

Иллюстрации

Показать всеРеферат

s(ОПИСАНИ

ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ

Союэ Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 12.1.1971 (№ 160824О/18-24) с. присоединением заявки №

Приоритет

Комитет по делам изобретений и открытий

:при Совете Министров

СССР

Опубликовано 28.XII.1972. Бюллетень № за 197

Дата опубликования описания 2.III.1973

88.8) Авторы изобретения

В. И. Гришенков и С. М. Тонконог

Заявитель

ФУНКЦИОНАЛЪНЪ|Й ПРЕОБРАЗОВАТЕЛЬ

Предлагаемое устройство может быть использовано в вычислительных устройствах для нелинейного преобразования цифровых величин.

Известны функциональные преобразователи цифровых величин, использующие принцип кусочно-линейной аппроксимации нелинейной функции. Они содержат приемный регистр, схему декодирования, схему памяти, делительный счетчик и преобразователь кода.

Их недостатком является низкое быстродействие преобразования заданной функции.

В предлагаемом устройстве использован преобразователь параллельного кода в последовательность импульсов, входные шины которого присоединены к младшим разрядам приемного регистра. Выход преобразователя подключен к счетному входу делительного счетчика, выход которого соединен со счетным входом реверсивного регистра.

Это позволяет ускорить преобразование цифровых величин, так как путем расшифровки состояния старших разрядов приемного регистра кода аргумента определяется значение функции, соответствующее началу линейного участка аппроксимации, а время преобразования в пределах этого участка зависит от его величины по оси аргумента и достаточно мало.

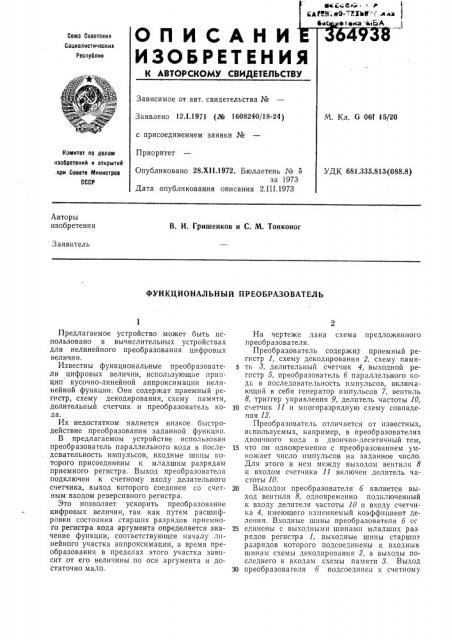

На чертеже дана схема предложенного преобразователя.

Преобразователь содержит приемный регистр 1, схему декодирования 2, схему памя5 ти 8, делительный счетчик 4, выходной регистр 5, преобразователь 6 параллельного кода в последовательность импульсов, включающий в себя генератор импульсов 7, вентиль

8, триггер управления 9, делитель частоты 10, 10 с етчик 11 и многоразрядную схему совпадения 12.

Преобразователь отличается от известных, используемых, например, в преобразователях двоичного кода в двоично-десятичный тем, 15 что он одновременно с преобразованием умножает число импульсов на заданное число.

Для этого в нем между выходом вентиля 8 и входом счетчика 11 включен делитель частоты 10.

2о Выходом преобразователя 6 является выход вентиля 8, одновременно подключенный к входу делителя частоты 10 и входу счетчика 4, имеющего изменяемый коэффициент деления. Входные шины преобразователя 6 сс

25 единены с выходными шинами младших разрядов регистра 1, выходные шины старишх разрядов которого подсоединены к входным шинам схемы декодирования 2, а выходы последнего к входам схемы памяти 8. Выход

30 преобразователя 6 подсоединен к счетному

364938 входу счетчика 4, выход которого подсоединен к счетному входу регистра 5. Один выход схемы памяти 8 подключен к управляющему входу регистра 5, а каждый остальной — к управляющему входу счетчика 4 и к одному входу установки регистра 5, что обеспечивае запись значения функции, соответствующего начальной точке определенного линейного участка аппроксимации.

Функциональное преобразование числовой величины N, представленной кодом, сводится к преобразованию кодов в последовательность импульсов, делению последних на величину М;, обратную угловому коэффициенту

1-го линейного участка аппроксимации и к суммированию результатов деления и значения функции в начальной точке ломанной кривой F (N,, ). Преобразование заканчивается в момент равенства числа импульсов последовательности значению преобразуемого кода.

Преобразователь работает следующим обр азом.

После установки схемы в исходное состояние и записи кода входного числа NÄ в приемный регистр 1 производится определение линейного участка аппроксимации схемой декодирования 2, запись значения F(N„ ) в регистре 5 и установка коэффициента деления, соответствующего данному линейному участку., в счетчике 4 с помощью схемы памяти 8.

По сигналу с отдельного выхода схемы памяти 3 регистр 5 включается в режим суммирования. Подачей пускового импульса на единичный вход триггера управления 9 устанавливают последний в пропускное для вентиля 8 состояние, и импульсы с выхода генератора импульсов 7 начинают поступать одповременно на счетные входы счетчика 4 и делителя частоты 10.

С выхода счетчика 4 импульсы поступают на счетный вход регистра 5, где суммируют5 ся с записанным значением F(N,. ). Процесс суммирования прекращается, как только содержимое счетчика 11 станет равным содержимому младших разрядов регистра 1, подсоединенных к выходам схемы совпадения 12.

При этом сигналом с выхода схемы совпадения 12 триггер управления 9 устанавливаетс» в непропускное для вентиля 8 состояние.

Значение функции F(N,,) снимается с регистра 5.

При функциональном преобразовании в соответствии с знакопеременными функциями схема памяти должна обеспечивать запоминание знака функции и коммутацию триггера знака выходного регистра. го

Предмет изобретения

Функциональный преобр азователb, содержащий приемный регистр, старшие разряды которого подключены к входным шинам схемы

25 декодирования с присоединенной к ее выходу схемой памяти, делительный счетчик, соединенный управляющими входами с выходами схемы памяти, которые подключены к управляюн ему и установочным входам реверсив30 ного регистра, и преобразователь параллельного кода в последовательность импульсов, отличающийся тем, что, с целью повышения быстродействия, в нем входные шины преобразователя параллельного кода в последова35 тсльность импульсов присоединены к младшим разрядам приемного регистра, а его выход подключен к счетному входу делительного счетчика, выход которого соединен со счетным входом реверсивного регистра.

364938

q (Nx) б !

1 !

) !

Составитель О. Сахаров

Техред Л. Богданова

Редактор Л. Утехина

Корректоры: А. Дзесова и T. Гревцова

Типография, пр. Сапунова, 2

Заказ 377/14 Изд. № 112 Тираж 647 Подписное

Ц11ИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4 5