Интерполятор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 364943

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 27ЛЧ.1971 (№ 1648839/18-24) с присоединением заявки ¹

Приоритет

М. Кл. G 06g 7/3 0

Комитет ио делам изобретений и открытий при Совете Министрое

СССР

УДК 681.335.87(088.8) Опубликовано 28.XII 1972. Бюллетень № 5 за 1973

Дата опубликования описания З.IV.1973

Лвтор изобретения

В. Н, Коробейников

Ордена Ленина институт кибернетики AH Украинской ССР

Заявитель

ИНТЕРПОЛЯТОР

Изобретение относится к области вычислительной техники и может быть применено для воспроизведения функций, зависящих от времени, при выходе информации на электроннолучевые трубки, графопостроители и исполнительные механизмы в управляющих вычислительных системах.

Известен интерполятор, построенный на базе интегрирующего усилителя и ключевой схемы.

Его недостатком является низкая точность воспроизведения функций.

С целью повышения точности предлагаемый интерполятор содержит аналоговое запоминающее устройство, вход которого соединен через ключ с выходом сумматора, а выход подключен ко входу интегратора.

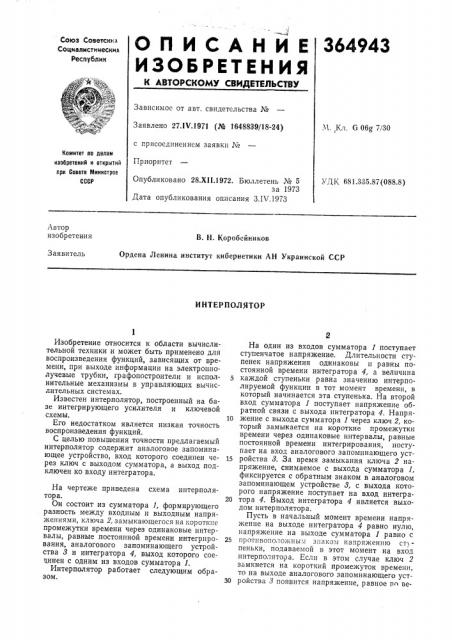

На чертеже приведена схема интерполятора.

Он состоит из сумматора 1, формирующего разность между входным и выходным напряжениями, ключа 2, замыкающегося на короткие промежутки времени через одинаковые интервалы, равные постоянной времени интегрирования, аналогового запоминающего устройства 8 и интегратора 4, выход которого соединен с одним из входов сумматора 1.

Интерполятор работает следующим образом.

На один из входов сумматора 1 поступает ступенчатое напряжение. Длительности ступенек напряжения одинаковы и равны постоянной времени интегратора 4, а величина

5 каждой ступеньки равна значению интерполируемой функции в тот момент времени, в который начинается эта ступенька. На второй вход сумматора l поступает напряжение обратной связи с выхода интегратора 4. Напря10 жение с выхода сумматора 1 через ключ 2, который замыкается на короткие промежутки времени через одинаковые интервалы, равные постоянной времени интегрирования, поступает на вход аналогового запоминающего уст15 ройства 8. 3а время замыкания ключа 2 напряжение, снимаемое с выхода сумматора 1, фиксируется с обратным знаком в аналоговом запоминающем устройстве 8, с выхода которого напряжение поступает на вход интегра20 тора 4. Выход интегратора 4 является выходом интерполятора.

Пусть в начальный момент времени напряжение на выходе интегратора 4 равно нулю, напряжение на выходе сумматора 1 равно с

25 противоположны;t знаком напряжению ступеньки, подаваемой в этот момент на вход интерполятора. Если в этом случае ключ 2 замкнется на короткий промежуток времени, то на выходе аналогового запоминающего устЗО ройства 8 появится напряжение, равное rrn ве364943

Предмет изобретения

)) г !

Составитель О. Сахаров

Техред Л. Грачева

Корректоры И. Божко и H. Прокуратова

Редактор Л. Утехина

Заказ 728/2 Изд. ¹ 175 Тираж 647 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 личине и по знаку напряжению на входе интерполятора. Это напряжение поступает на вход интегратора 4, на выходе которого образуется линейно изменяющееся напряжение, угол наклона которого пропорционален величине постоянного входного напряжения. Через время, равное длительности ступеньки, на выходе интегратора 4 будет напряжение, равное по величине и противоположное по знаку напряжению на входе интерполятора в начальный момент времени. Если в течение этого времени напряжение на входе интерполятора не изменилось, то на выходе сумматора

1 устанавливается напряжение, равное нулю, и через ключ 2 в аналоговое запоминающее устройство 8 так же запишется нуль, т. е. в этом случае напряжение на выходе интегратора 4 останется постоянным. Такое состояние продолжается до тех пор, пока напряжение на входе интерполятора не изменится.

Как только произойдет изменение напряжения на входе интерполятора, на выходе сумматора 1 получается разность между входным напряжением интерполятора и напряжением с выхода интегратора 4. После очередного замыкания на короткое время ключа 2 на выходе аналогового запоминающего устройства 8 получается эта разность с обратным знаком, т. е. истинное значение приращения интерполируемой функции. Это прира5 щение интегрируется интегратором 4, и весь процесс продолжается с периодом, равным постоянной времени интегрирования. При этом на выходе интегратора 4 образуется кусочнолинейное напряжение, которое интерполирует

10 значение функции между последовательными отсчетами.

Отличительной особенностью интерполятора является наличие отрицательной обратной связи, позволяющей избежать накапливания

15 ошибок.

Интерполятор, содержащий ключ и сумма20 тор, один из входов которого присоединен к выходу интегратора, отличающийся тем, что, с целью повышения точности, он содержит аналоговое запоминающее устройство, вход которого соединен через ключ с выходом сум25 матора, а выход подключен ко входу интегратора а.