Синхронно-фазовый демодулятор сигналов с частотной модуляцией

Иллюстрации

Показать всеРеферат

Рг г

ARi

Ои =л иоте.

О П И НЯЕ

ИЗОБРЕТЕНИЯ

3650I3 саюа Соеетскил

Социалистические

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 08.11.1971 (№ 1628743/26-9) М. Кл. Н ОЗЬ 3/04

Н 03d 13/00 с присоединением заявки ¹

Комитет ао делам изобретений N открытий ари Сосете Мииистрое

СССР

Приоритет

УДК 621.396.662 (088.8) Опубликовано 28.Х11.1972. Бюллетень № 5 за 1973

Дата опубликования описания 24ХП1.1973

Авторы изобретения

Н. М. Фролова, Ю. Ф. Урядников и В. Е. Предтеченский

Заявитель

СИ НХРОННО-ФАЗОВЫЙ ДЕМОДУЛЯТОР СИ ГНАЛОВ

С ЧАСТОТНОЙ МОДУЛЯЦИЕЙ

Изобретение относится к радиотехнике.

Известны синхронно-фазовые,демодуляторы сигналов с частотной модуляцией, содержащие последовательно соединенные фазовый детектор, второй вход которого соединен с источником входного сигн|ала, фильтр нижних частот, узкополосный фильтр нижних час= тот, схему индикации синфазного состояния, генератор поиска, схему,па мяти, сумматор, подключенный также к выходу фильтра нижних частот, частотно-,модулированный генератор, подключенный ко второму входу фазового детектора,.

Цель изобретения — исключение динамической расстройки частоты.

Предлагаемый демодулятор отличается тем, что между схемой индикации си нфазного состояния и вторым входом схемы памяти включено управляемое разрядное устрой ство.

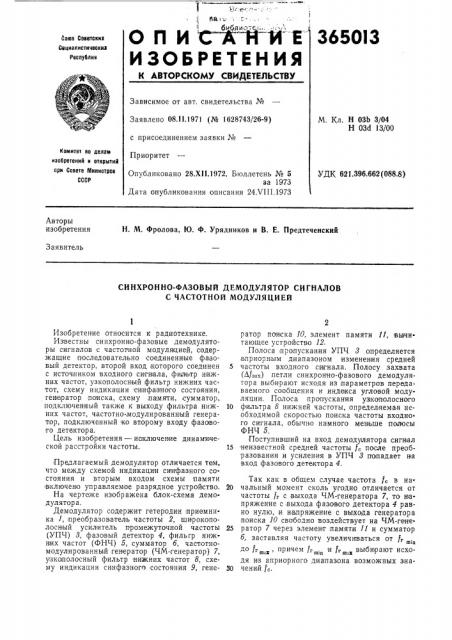

На чертеже изображена блок-схема демодулятор а.

Демодулятор содержит гетеродин привмника 1, преобразователь частоты 2, широкополосн ый усилитель промежуточной частоты (УПЧ) 3, фазовый детектор 4, фильгр нижmx частот {ФНЧ) 5, сумматор б, частотномодулированный генератор (ЧМ-генератор) 7, узкополосный фильтр нижних частот 8, схему индикации синфазного состояния 9, генератор поиска 10, элемент памяти 11, вы читающее устройство 12.

Полоса пропускания УПЧ 8 определяется априорным диапазоном изменения средней

5 частоты входного сигнала. Полосу захвата

{af3Qx):петли синхронно-фазового демодулятора выбирают исходя из параметров переда= ваемого сообщения и индекса угловой модуляции. Полоса пропускания узкополосного

i0 фильтра 8 нижней частоты, определяемая необходимой скоростью поиска частоты входно* го ситнала, обычно намного меньше полосы

ФНЧ 5.

Поступивший на вход демодулятора сигнал

15 неизвестной средней частоты f, после преобразования и усиления в УПЧ 3 попадает на вход фазового детектора 4.

Так как в общем случае частота 1, в на20 чальный момент сколь угодно отличается от частоты 1г с выхода ЧМ-генератора 7, то вапряжение с выхода фазового детектора 4 равно нулю, и напряжение с выхода генератора поиска 10 свободно воздействует на ЧМ-гене2s ратор 7 через элемент:памяти 11 и сумматор б, заставляя частоту увеличиваться от f, г mIq до /,,, причем /,, и /г, выби|рают исходя и з априорного диапазона возможных зна30 чений /,.

365013

Когда,=,— Afeard на выходе фазового детектора 4 появляется положительн|ое напряжение, которое, действуя через ФНЧ 5 и сумматор б на ЧМ-генератор 7, переводит петлю синхронизации, в режим захвата, и f„становится равна f,. Однако напряжение с выхода генератора поиска 10 продолжает воздейст=вовать на ЧМ генератор 7 через сумматор б и элемент памяти 11 в прежнем направлении, стремясь увеличить f„. Это воздействие приводит к тому, что н апряжение с выхода фазового детектора 4:понижается на величину, равную повышению н апряжения с выхода тенератора 10, и f, остается равной f<.

Когда на пряжение с выхода фазового де= тектора 4, уменьшаясь, переходит через нуль, схема инди1кации синфазности 9 выдает команду н а остановку и отключение генератора 10 и подключение,вычитающего устройства 12. С этого момен та схема работает в нор= мальном режиме детектирования угловой MO" дуляци и си гнала, как схема фазовой автоподстройки частоты без начальной расстройки.

При этом выходное напряжение, несущее ин= формацию о сообщении, снимается с ФНЧ 5.

Таким образом, в момент вхождения в режим нормальной работы схема обладает высокой помехоустойчивостью, определяемой полосой узкополосного фильтра 8 нижних частот, соота вляющих единицы герц.

При постоянстве частоты f, действие вычи= тающего устройства 12 приводит к тоху, что на пряжение с элемента памяти 11 уменьша= ется, заставляя f, тоже уменьшаться, на выходе фазового детектора 4 .появляется положительное напряжение, которое компен|сирует это уменьшение и включает схему индикации си нфазного состояния 9, которая вновь под= ключает генератор 10 к элементу памяти, возвращая схему в исходное состояние. Таким обра зом, f, все время поддерживается равной средней частоте f, à, рабочая точка — в нулевом положении.

При уходе, средней частоты f, демодулятор работает следующим образом.

Допустим, f, начинает увеличиваться. Тогда на выходе фа зового детектора 4 появляет= ся положительное на пряжение, и схема и ндикации сияфазности 9 подключает генератор 10

5 к ЧМ-генератору 7 через элемент памяти 11 и сумматор б, заставляя f, тоже увеличиваться. Как только f, становится равно f<, генератор 10 отключается и так далее. Таким образом, этот режим работы отличается от ре10 жи.ма работы при постоянной 1, только увеличением частоты подключений генератора 10 к элементу памяти 11. При уменьшении частота подключений соответственно уменьшается.

15 Такая ра,бота устройства возможна благодаря тому, что на ЧМ-генератор 7 воздействуют две противоположные тенденции: генератор .поиска старается изменить частоту ЧМгенератора в одну сторону, а вычитающее

20 устройство — la другую. В результате этого при любых изменениях средней частоты сигнала f, устройство работает в режиме .сии= хронно-фазового детектирования с нулевой рабочей точкой, реализуя максимальную по25 мехоустойчивость.

Предмет изобретения

30 Син|хронно-фазовый демодулятор сигналов с частотной модуляцией, содержащий последовательно соединенные фазовый детектор, второй вход которого соединен с источником входного сигнал а, фильтр нижних частот, уз35 кополосный фильтр нижних частот, схему индикации син фазного состояния, генератор поиска, схему памяти, сумматор, подключенный также к выходу фильтра нижних частот, частотно-модулированный генератор, подклю40 ченный ко второму входу фазового детектора, отлича ощийся тем, что, с целью исключения динамической расстройки частоты, между схемой индикации синфазного состояния и вторым входом схемы памяти включено уп45 равляемое разр ядн ое устройство.

365013

Составитель Ю. Еркин

Техред Л. Богданова

Редактор В. Федотов

Корректор E. Зимина

Типография, пр. Сапунова, 2

Заказ 2289/1 Изд. R 597 Тираж 780 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Я-35, Раушская наб., д. 4/5