Устройство для приема сигналов с частотно-фазовой манипуляциейли- '*"^<*"i'^.'''*>& г •'^••ta:'- «i"*" v•''i - *.v.'v/!'wor..'ehth04e;••cm

Иллюстрации

Показать всеРеферат

367562

ОПИСАН ИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 11.Ч11.1970 (№ 1455197/26-9) с присоединением заявки №

Приоритет

Опубликовано 23Л.1973. Бюллетень № 8

Дата опубликования описания 13.III.19?3

М. Кл. Н 041 27/18

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 621.391.174 (088.8) Авторы изобретения Н. С. Мамаев, И. Н. Кычкин, В. И. Назаров, В. В. Борецкий и О. Г. Безвиконный

Заявитель

УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ

С ЧАСТОТНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ

Известны устройства для приема дискретных сигналов в каналах частотно-фазовой телеграфии, содержащие фильтры, частотный и фазовый демодуляторы, блок декодирования, систему синхронизации, регенератор, сумматор скачков частоты и фазы и разделитель сигналов.

Недостаток известных устройств состоит в том, что они не обеспечивают требуемой точности демодуляции.

Для повышения точности демодуляции в предлагаемом устройстве к выходу фильтра колебаний первой частоты подключены параллельно частотный и фазовый демодуляторы, к выходам которых подключены соединенные последовательно формирователь импульсов и собирательный каскад с элементом задержки на половину бинарного знака, а к выходу фильтра колебаний второй частоты подключены параллельно частотный и фазовый модуляторы с формирователями импульсов, соединенные с сумматором. При этом на выходе сумматора устройства включены последовательно элемент задержки и разделитель сигналов.

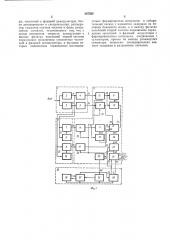

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 — фазовременные диаграммы, поясняющие работу устройства.

Устройство состоит из частотного демодулятора 1, включающего полосовой фильтр 2 частоты f, полосовой фильтр 8 частоты f2, частотные детекторы 4 и 5; фазового демодулятора б, содержащего фазовые детекторы 7 и 8 для колебаний с частотами fi и /2 соответст5 венно, линии 9 и 10 задержки сигналов с частотой f и f2 соответственно на время, равное половине длительности то элементарной посылки; блока 11 декодирования, включающего формирователя 12 и 13 импульсов скачков

10 продетектированного соответствующим частотным детектором напряжения, формирователи 14 и 15 импульсов скачков фазы сигналов с частотой f и f2 соответственно, линии 1б и 17 задержки импульсов на 0,5 тс, логические

15 элементы «ИЛИ» 18 и 19, усилитель 20, сумматор 21 импульсов скачков частоты и фазы, на выходе которого включены последовательно элемент 22 задержки на 0,5 то (триггер содним устойчивым состоянием), регенератор 28

20 и разделитель 24 информационных каналов.

Узел 25 формирования сигнала тактовой синхронизации включает генератор 2б удвоенной тактовой частоты 2Fp, элемент 27 коррек1 ции частоты F,= — синхросигнала, устройстт о во 28 сравнения синхросигнала и сигнала на выходе регенератора, формирователь 29 импульсов с тактовой 1с и удвоенной тактовой

30 21 с частотами синхронизации.

367562

На фазовременных диаграммах (см. фиг. 2) приняты следующие обозначения:

80 — символы передаваемого сообщения;

81 — посылки сигнала с частотой f на входе приемного устройства;

82 — посылки сигнала с частотой f на входе приемного устройства;

88 — сигнал на выходе частотного детектора 4;

84 — сигнал на выходе частотного детектора 5;

85 — синхроимпульсы с удвоенной тактовой частотой 2РО, 86 — импульсы скачков частоты сигнала 83;

87 — импульсы 86, задержанные на О,о тв, 88 — сигнал на выходе логического элемента «ИЛИ» 18;

89 — импульсы скачков частоты сигнала 84;

40 — сигнал на выходе фазового детектора 7;

41 — импульсы скачков фазы сигнала 31;

42 — импульсы 41, задержанные на 0,5 Fo, 43 — сигнал на выходе логического элемента «ИЛИ» 19;

44 — сигнал на выходе фазового детектора 8;

45 — импульсы скачков фазы сигнала 82;

46 — импульсы скачков фазы принимаемого сигнала;

47 — сигнал на выходе сумматора 21;

48 — сигнал на выходе триггера 22 и регенератора 28;

49 — символы принятого сообщения;

50 — синхроимпульсы с тактовой частотой Fo,.

5l — символы сообщений 1 канала;

52 — символы сообщений II канала, Те же обозначения на блок-схеме устройства (см. фиг, 1) показывают прохождение соответствующих сигналов между элементами схемы.

Принятый сигнал с комбинированной частотно-фазовой манипуляцией двух колебаний с произвольным и независимым разносом несущих частот после фильтрации в полосовых фильтрах 2 и 8 поступает одновременно на частотные детекторы 4 и 5 и фазовые детекторы 7;8.

Продетектированные частотными детекторами 4 и 5 напряжения 88 и 84 поступают на входы формирователей 12 и 13 импульсов скачков частоты сигнала соответственно.

Последовательность импульсов 86 скачков продетектированного напряжения 88 сигнала

81 с первой частотой f< подвергается логической обработке при помощи логического элемента «ИЛИ» 18, первый вход которого соединен с формирователем 12 непосредственно, а второй вход — через линию 16 задержки импульсов сигнала Зб на 0,5 тю. После этого сигнал 88 с выхода логического элемента «ИЛИ»

18 поступает на первый вход сумматора 21.

Последовательность импульсов 89 скачков продетектированного напряжения 84 сигнала

4

82 со второй частотой f» поступает,на второй вход сумматора 21.

Импульсы 86; 89 соответствуют скачкам (смене) частот сигналов 81; 32 на границах кодовых групп.

Для обнаружения скачков фазы принятых колебаний 31 и 82 производится перемножение этих сигналов на фазовых детекторах 7 и

8 с линиями 9 и 10 задержки на О,о тр, на их вторых входах. Продетектированные фазовыми детекторами 7 и 8 напряжения 40 и 44 поступают соответственно на входы формирователей 14 и 15 импульсов скачков фазы сигналов с частотами f< и fz.

Последовательность импульсов 41 скачков напряжения продетектированного напряжения

40 сигнала 81 с первой частотой f< подвергается логической обработке при помощи логического элемента «ИЛИ» 19, первый вход которого соединен с формирователем 14 непосредственно, а второй вход — через элемент 17 задержки импульсов сигнала 41 на 0,5тр. После этого сигнал 48 с выхода логического элемента «ИЛИ» 19 поступает на третий вход сумматора 21.

Последовательность импульсов 45 скачков продетектированного напряжения 44 сигнала

82 со второй частотой / поступает на четвертый вход сумматора 21.

Импульсы 41; 45 и 46 соответствуют скачкам фазы сигнала 31; 82 на границах кодовых групп, На выходе сумматора 21 образуется последовательность 47 импульсов, характеризующая скачки 88; 39 частоты и 46 фазы принятого сигнала, из которой с помощью триггера

22 с одним устойчивым состоянием и регенератора 28 получается сигнал 48 в виде потенциальной формы передаваемого сообщения 80.

Разделитель 24 информационных каналов преобразует последовательность символов 49 принятого сообщения в две параллельные последовательности 51 и 52 символов сообщений

1 и II каналов.

Синхроимпульсы 35 с удвоенной тактовой частотой 2Fp синхронизации подаются с выхода формирователя 29 на вторые входы формирователей 12;18;14; 15, регенератора 28 и разделителя 24, а синхроимпульсы 50 с тактовой частотой Fo — на третий вход разделителя 24.

Предмет изобретения

Устройство для приема сигналов с частотнофазовой манипуляцией, сформированных при манипуляции двух независимых по фазе колебаний с произвольным разносом частот, при которой комбинация сигналов из двух единиц с произвольным числом нулей передается на первой частоте, комбинация сигналов из единицы и нуля с произвольным числом нулей передается на второй частоте, а при повторении указанных комбинаций фаза излучаемых колебаний переворачивается на границах одноименных комбинаций, содержащее фильт367562

1 Г7/

1 1

Ф г 1 ры, частотный и фазовый демодуляторы, олоки декодирования и синхронизации, регенератор, сумматор скачков частоты и фазы, разделитель сигналов, отличающееся тем, что, с целью повышения точности демодуляции к выходу фильтра колебаний первой частоты параллельно подключены упомянутые частотный и фазовый демодуляторы, к выходам которых подключены соединенные последовательно формирователь импульсов и собирательный каскад с элементом задержки на половину бинарного знака, а к выходу фильтра колебаний второй частоты подключены парал5 лельно частотный и фазовый. модуляторы с формирователями импульсов, соединенные с сумматором, причем на выходе упомянутого сумматора включены последовательно элемент задержки и разделитель сигналов.

l

1

1 !

l

I

I

1

1

1-!

367562 г

5о

51

Фиг. 2

Составитель М. Мермаи

Техред Л. Грачева

Редактор Г. Котельский

Корректоры: А. Степанова и Е. Сапунова

Заказ 49б/9 Изд. № 1147 Тираж б78 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, )К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2