Устройство для преобразования логических

Иллюстрации

Показать всеРеферат

nгч о и и с д Й-и-е

ИЗОБРЕТЕНИЯ

К АВТОИ:КОМУ СВИДЕТЕЛЬСТВУ

368594

Союэ Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 31.Х11.1970 (№ 1616105/18-24) с присоединением заявки №

Приоритет

Опубликовано 26.1.1973. Бюллетень № 9

М. Кл. О 06f 3/04

Комитет по делам иаобретеиий и открытий ори Совете тлиииотроа

СССР

УДК 681.332.65(088.8) Дата опубликования описания 27.П1.1973

Авторы изобретения Г. А, Кузьмин, В. М. Миролюбский, В.:И, Редченко, Л. А. Сулима и О. К. Левшин

Заявитель

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЛОГИЧЕСКИХ

УРОВНЕЙ

Изобретение относится к области вычислительной техники и автоматики и предназначено для использования во вводных устрой.ствах ЭЦВМ.

Известные устройства для преобразования .логических уровней, содержащие входные трансформаторы, вторичные обмотки которых соединены с триггерами разрядов единицы и,нуля и синхроимпульсов с раздельными входа,ми, выходы которых через логический блок:соединены со входами выходного ,регистра, не обладают достаточной надежностью работы в сложных эксплуатационных условиях, требуя достаточно жесткой синхронизации информационных и тактовых импульсов, что сужает область их применения.

Предложенное устройство отличается тем, что логический блок содержит ячейки «И», «ИЛИ», триггер и инвертор, причем единичные выходы триггеров разрядов единицы и нуля соединены через ячейки «И», вторые входы которых соединены с единичным выходом триггера синхроимпульсов, непосредственно с единичным и нулевым входами выход ного регистра, и через дополнительные ячейки «И» и ячейку «ИЛИ» соединены со сдвигающим входом выходного регистра, единичных входом триггера и входом инвертора.

Выходы триггера и инвертора через ячейку

«И» соединены с нулевыми входами триггеров единицы, нуля и синхропмпульсов. Вторые входы дополнительных ячеек «И» и нулевой вход триггера соединены с выходом ячейки «ИЛИ», соединенной своими входами со вторичными обмотками входных трансформаторов.

Это позволяет расширить область применения и повысить надежность работы устройства.

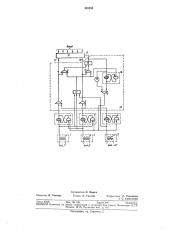

M На чертеже показана функциональная схема устройства.

Оно содержит входные трансформаторы

1 — 8, триггеры 4 — б соответственно разрядов

«1», и «О» и синхроимпульсов, ячейки «И» 7

15 п 8, дополнительные ячейки «И» 9 и 10, ячейки «ИЛИ» 11 и 12, инвертор И, триггер 14, ячейку «И» 15 и выходной регистр 1б с единичным 17, нулевым 18, сдвигающим 19 входами и логический блок 20.

20 Устройство работает следующим образом.

Вследствие различных временных задержек в линиях связи и входных трансформаторах

1 — 8, а также несинхронности передающих и приемных устройств импульсы входной пн25 формация, например парафазного кода, могут опережать или отставать от сопровождающих cHHxPQHAIIIA 1bcoB. Ес 7H HIIIII Ibc входной цифровой информации на входах «1» или

«О» опережает тактовый спяхропмпульс

30 «СИ», передний фронт этого входного им368594

Зо

3 пульса, проходя через ячейку «ИЛИ» 11, опрокидывает в состояние «О» триггер 14, подготавливая входную часть схемы. Сразу же после этого происходит промежуточное запоминание входной информации, т. е. устанавливается в состояние «1» соответствующий триггер 4 или 5, подготавливая этим прохождение сигнала на входе соответствующей ячейки «И» 7 или 8 логического блока 20.

Одновременно подтверждается исходное нулевое состояние на триггер 5 при появлении сигнала на входе «1», или на триггере 4 при появлении сигнала на входе «О». При приходе тактового синхроимпульса «СИ» триггер б опрокидывается в состояние «1», запоминая этот синхроимпульс. Сигнал, соответствующий уровню «1» на выходе триггера б, разрешает прохождение сигнала с единичных выходов триггеров 4 или 5 через соответствующую ячейку «И» 7 или 8 на единичный или нулевой вход регистра 1б. Входная информация в этом случае переписывается в регистр 1б передним фронтом тактового синхроим пульса. Далее передний фронт синхроимпульса разрешает прохождение сигнала через ячейку «ИЛИ» 11 и через соответствующую ячейку «И» 9 или 10, а затем через вторую ячейку «ИЛИ» 12 передний фронт синхроимпульса поступает,на единичный вход триггера 14, устанавливая его в состояние «1». На все время действия тактового синхроимпульса «СИ» ячейки «И» 15 закрыта нулевым уровнем, поступающим на ее вход с инвертора 18. Задний фронт тактового синхроимпульса через ячейку «ИЛИ» 12 формирует сигнал сдвига на сдвигающем входе 19 регистра 1б и, через инвертор .18 и ячейку «И» 15 форми.рует сброс на нулевых входах триггеров 4 — б, после чего схема готова для приема следующих импульсов входной цифровой информации.

Если импульс входной цифровой информации .на входах «1» или «О» отстает от тактового синхроимпульса «СИ»,,передний фронт синхроимпульса через ячейку «ИЛИ» 11 опрокидывает в состояние «О» триггер 14, подготавливая входную часть схемы. Происходит промежуточное запоминание входной информации путем установки триггера б в состоя:ние «1», чем подготавливается прохождение сигнала на входах ячейки «И» 7, 8.

При приходе импульсов входной информации на входы «1», или «0» устанавливается в состояние «1» соответствующий триггер 4 или 5. Одновременно подтверждается исходное нулевое состояние на триггере 5 при появлении сигнала на входе «1» или на триггере 4 при, появлении сигнала на входе «О».

После установления одного из триггеров 4 или 5 в состояние «1» передним фронтом через соответствующую ячейку «И» 7 или 8 записывается входная информация на единичный 17 или нулевой 18 вход регистра 1б, и устанавливается в состояние «1» триггер 14.

Задним фронтом импульса входной информации формируется сигнал сдвига на сдвигающем входе 19 регистра 1б, после чего через инвертор 18 и схему 15 триггеры 4 — б устанавливаются в исходное состояние.

При одновременном приходе импульсов на входы «1» или «О» и «СИ» схема работает аналогично.

Предмет изобретения

Устройство для преобразования логических уровней, содержащие входные трансформаторы,,вторичные обмотки которых соединены с триггерами разрядов единицы,,нуля и синхроимпульсов с раздельными входами, выходы которых через логический блок соединены со входами выходного регистра, отличающееся тем, что, с целью расширения области применения и повышения надежности работы устройства, логический блок содержит ячейки

«И», «ИЛИ», триггер и инвертор; причем единичные выходы триггеров разрядов единицы и нуля соединены через ячейки «И», вторые входы которых соединены с единичным выходом триггера синхроимпульсов, непосредственно с единичным и нулевым входами выходного .регистра и через дополнительные ячейки, «И» и ячейку «ИЛИ» соединены со сдвигающим входом выходного регистра, единичным входом триггера и входом инвертора, а выходы триггера и инвертора через ячейку

«И» соединены с нулевыми входами триггеров единицы, нуля и синхроимпульсов, вторые входы дополнительных ячеек «И» и нулевой вход триггера соединены с .выходом ячейки «ИЛИ», соединенной своими входами со вторичными обмотками входных трансформаторов.

368594

1

Ф!

1 I

I

I

I! ро !

I

ga. си а 1.!

Вход.д

Составитель О. Поваго

Техред Л. Грачева

Редактор Л. Утехина

Корректоры: Е. Талалаева и С. Сатагулова

Заказ 6!9/5 Изд. ¹ 185 Тираж 647 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4, 5

Типография, пр. Сапунова, 2