Логический элемент

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

3697I4

Союз Со.-зтскиа

Социалистическиа

Республик

Зависимое от авт. свидетельства N

Заявлено 15Х11.1971 (№ 1679711/26-9) с присоединением заявки М

Приоритет

Опубликовано 08.11.1973. Бюллетень М 10

Дата опубликования описания 23.IV.1973

М. Кл. Н 03k 19;08

Комитет по делам изобретений и открытиЯ пр» Совете Министроа

СССР

УДК 681.325.65(088.8) Авторы изобретения

Ю. Е. Наумов и И. Ф. Пучков

Московский ордена Ленина авиационный институт им. Серго Орджоникидзе

Заявитель

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к цифровой технике.

Известен логический элемент, содержащий входной многоэмиттерный транзистор, соединенный коллектором с базой ключевого транзистора, коллектор которого подключен ко входу инвертора, и дополнительный транзистор.

Недостатком известного устройства является его малая помехоустойчивость, С целью повышения помехоустойчивости в предлагаемый логический элемент введен резистивный делитель, у которого первый выход соединен с эмиттером ключевого транзистора, а,второй выход — с коллектором дополнительного транзистора, подключенного базой через резистор к выходу инвертора.

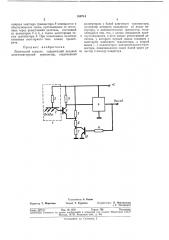

На чертеже дан предлагаемый логический элемент.

Устройство содержит лотическую часть 1, выполняющую функцию TL, собранную на многоэмиттерном транзис-.оре 2 и резисторе 8, инвертор 4, резистивный делитель, состоящий из резисторов 5, б и 7, ключевой транзистор 8, включенный по схеме с общим эмиттером, в колле кто рную цепь которого включен резистор 9, и дополнительный транзистор 10, подключенный через резистор 11 к выходу схемы.

Ключевой транзистор 8 соединен базой с коллектором многоэмиттерного транзистора 2, коллектором — с инвертором 4, а эмиттером — со средней точкой между резисторами

5 и б. Дополнительный транзистор 10 коллектором подключается к средней точке между резисторами б и 7.

5 Устройство работает следующим образом.

Если на одном из входов имеется низкий уровень напряжения (логический «О»), то многоэмиттерный транзистор 2 находится в насыщении, потенциал коллектора выше по10 тенциала эмиттера на величину напряжения насыщения транзистора. В этом режиме потенциал эмиттера ключевого транзистора 8 выбирается резистивным делителем, состоящим из резисторов 5, б и 7, таким, что его

15 эмиттерный переход закрыт; в результате на инвертор 4 с коллектора ключевого транзистора 8 подается высокий уровень, инвертор открывается и на его выходе устанавливается низкий уровень, при этом дополнительный

20 транзистор 10 закрывается.

Если на всех входах схемы повысить напряжение, то пропорционально повышается напряжение на коллекторе транзистора 2 и на базе транзистора 8.

25 При некоторой величине напряжения транзистор 8 начинает открываться, потенциал его коллектора понижается и приводит к закрыванию инвертора 4. Высокое напряжение на выходе схемы обеспечивает открывание тран30 зистора 10 и шунтирование резистора 7. По369714 од

Составитель А. Белов

Техред Т. Курилко Корректоры: Л. Новожилова и Г. Запорожец

Редактор Т. Морозова

Заказ 1077/11 Изд. № 1270 Тираж 780 Подписное

Ц11ИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, %-35, Раушская наб., д. 4(5

Типография, пр. Сапунова, 2 тенциал эмиттера транзистора 8 понижается и обеспечивается током, протекающим от источника через резистивный делитель, состоящий из резисторов б и б, а также эмиттерным током транзистора 8. При низкоомном делителе влиянием эмиттерного тока можно пренебречь.

Предмет изобретения

Логический элемент, содержащий входной многоэмиттерный транзистор, соединенный коллектором с базой ключевого транзистора, коллектор которого подключен ко входу инвертора, и дополнительный транзистор, отличающийся тем, что, с целью повышения поме5 хоустойчивости, в него введен резистивный делитель, у которого первый выход соединен с эмиттером ключевого транзистора, а второй выход — с коллектором дополнительного транзистора, подключенного своей базой через ре10 зистор к выходу инвертора.