Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

O 11 И С А И И Е,3EI664

И ЗО ВРЕТЕ Н ИЯ

Союз Соеетокик

Социалистических

Республик тт АЗОРСКОМУ СВИДБ ЕЛЬ С7ВУ

Зависимое от авт. свидетельства Х

М. Кл. Н 03f 3/ 34

Заявлено 20Х.1971 (№ 1659160/26-9) с присоединением заявки №вЂ”

Коотитвт по делам иаооретвмий и открьпии ври Совете Миииотров

6СР

IIp: орптет

УДК 621.375.024 (088.8) Оп, бликовано 22.11.1973. БючлстсlIh ¹ 1-2

Дата опубликов",íèÿ описания 18.V11.1973

И. А. Аракчеева, Л. П. Домнин, В. И. Никишин, Г. С. Остапенко, Л. Р. Портянский, A. C. Савлук, С. С, Соболев и А. П. Удовик

Лвторгя изобрстсп я

Заявитель

ДИФФЕРЕНЦИАЛ ЬНЫ Й УСИЛ ИГЕЛ Ь

Изооретение относится к транзисторным дифференциальным усилителям, которые могут быть использованы в аналоговой вычислптельно "I технике, в усилителях следящих систем, в операционных усилителях.

Известные дифференциальные усилители, содержащие в каждом плече входной каскад на эмиттерпом повторителе с динамической нагрузкой и стабилизатором тока в цепи эмиттера динамической нагрузки и выходной каскад IIa эмиттерпых повторителях, имеют неболыпое входное сопротивление и невысокий коэффициент усиления.

Целью изобретения является увеличение входного сопротивления и коэффициента усиления усилителя.

Для достижения этой цели коллектор транзистора динамической нагрузки выходного каскада одного плеча соединен со средней точкой резисторпого делителя коллекторного питания транзистора динамической нагрузки входного каскада противоположного плеча, а база соединена с коллектором транзистора входного каскада противополоокного плеча, при этом эмиттеры транзисторов динамической нагрузки выходного каскада подключены через резистивную Т-образную цепочку к стабилизатору тока.

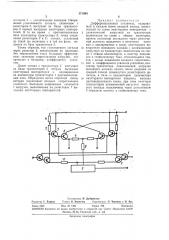

На чертеже показана

2 схема предлагаемого дифференциального усилителя.

В каокдом плече симметричного дифференциального усилителя включено четыре транзистора. Входные эмнттерные повторители

«ыполнепы па транзисторах 1, эмиттеры которы: соед IneIIII с базами транзисторов 2 — усп, гител ьных каскадов.

В коллгкторных цепях транзисторов ц Iключены по два резистора 8 и 4 и базы транзисторов 5 — первых каскадов выходных эмигтерных повторителей. Эмиттеры транзисторов 5 соедш;ены с оазамп транзисторов 6 — вторых каскадов выходных эмптгерных повторителей и с коллекторами трапзпсторов l противоположных плеч. Эмпттеры транзисторов 6 соединены между собой через резисторы 7, средняя точка которых через резистор 8 подключена к стабилизатору тока 9.

2З К последнему подключена также средняя î÷êà резисторов 10, включенных в эмпттерные цепи транзисторов 2. Средние точки резисторов 8, 4 подключены к коллекторам транзисторов 6 противополож,.ых плеч. Рези 5 сторы 4 и коллекторы транзисторов 5 подключены к источнику питания.

Усиливасмый сигнал подается в противофазе на входы транзисторов 1 — входных эмиттерных повторителей. С эмиттеров этих ,0 транзисторов сигнал проходит на базы транСоставитсль Н. Дубровская

Те»реп Я. Борисова Корректоры: Л, Чуркина и Н. Ау»

Редактор T. Ларина

Заказ 2443 Изд. № 1200 Тираж 780 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, )К-35, Раушская наб., д. 4/5

Загорская типография зисторов 2 — усилительных каскадов. Напряжение усиливаемого сигнала, снимаемое с резисторов 8, поступает на базы транзисторов 5 первых выходных эмиттерных повторителей. В то же время с противоположных плеч (коллектор транзистора б, точка соединения резисторов 8 и 4) сигнал, усиленный до такой хке величины и в той ке фазе, подается на базу транзистора 5.

Таким образом, ток усиливаемого сигнала через резистор 8, незначителен по величине.

Это эквивалентно очень большому эффективному значению сопротивления нагрузки, что приводит к большому коэффициенту усиления.

Далее сигнал с транзистора 5 поступает на базы транзисторов б вторых выходных эмиттерных повторителей и одновременно на коллекторы транзисторов 1 противоположных плеч. Образуется петля обратной связи, которая увеличивает входное сопротивление усилителя. Выходное напряжение снимается с нагрузок, выполненных на резисторах 7 выходных эмиттерных повторителей, Предмет изобретен и я

Дифференциальный усилитель, содержащий в каждом плече входной каскад, выполненный по схеме эмиттерного повторителя с

5 динамической нагрузкой на транзисторе; включенном по схеме с общим эмиттером; причем коллектор последнего через резисторный делитель подключен к источнику питания и одновременно к входу. эмиттерного по10 вторителя выходного каскада с динамической нагрузкой на транзисторе, включенном по схеме с общим коллектором, а эмиттер подключен к стабилизатору тока, отлачающийся тем, что, с целью повышения входного сопротивле15 ния и коэффициента усилениЯ усилителя, коллектор транзистора динамической нагрузки выходного каскада одного плеча соединен со средней точкой упомянутого резисторного делителя, а база †коллектором транзистора

20 эмиттерного повторителя входного каскада противоположного плеча, при этом эмиттеры транзисторов динамической нагрузки выходного каскада подключены через резистивную

Т-образную цепочку к стабилизатору тока.