Бсесоюснап -^ плтситио •<те;'ш1чес::лп

Иллюстрации

Показать всеРеферат

37254I

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 29.IX,1971 (№ 1702004/18-24) с присоединением заявки №

Приоритет

Опубликовано 01.Ш.1973. Бюллетень № 13

Дата опубликования описания 21 V.1973

М Кл G 05b 1/01

Комитет оо делам изобретений и открытий ори Совете Министров

СССР

УДК 621,375.026 (088,8) Авторы изобретения

А. И. Когут и В. М. Ситниченко

Заявитель

ДИСКРЕТНЫЙ НУЛЬ-ОРГАН

Предлагаемый дискретный нуль-орган предназначен для использования в ревероивных следящих системах дискретного типа, например, в дискретизованных системах реверсивного следящего электропривода.

Известны дискретные нуль-органы для следящих систем дискретного типа, содержащие блок фазовой ориентации импульсов, блок коммутации ориентированных импульсов и счетно-преобразовательный блок.

Предложенный нуль-ор|ган отличается тем, что он содержит триггеры и блоки переноса.

Пр|ичем первый и второй входы блока коммутации импульсов подключены к одному из выходов соответствующего триггера, третий и четвертый — к другому выходу этиках триггеров, два входа которых через соответствующие блоки переноса подключены ко входам входных синхронизаторов.

Это повышает точность ра боты устройства.

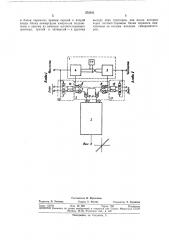

На чертеже изображена функциональная схема нуль-органа.

Нуль-ор ган содержит включенные функционально последовательно блок 1 фазовой ориентации импульсов, блок 2 коммутации импульсов, счетно-преобразовательный блок

8, выдающий в следящую систему сигнал рассогласования соответственно разности чисел импульсов и знакам задания и отработки.

Блок фазовой ориентации импульсов задания и отработки состоит из входных синхрони заторов 4 и 5, управляемых в противофазе тактовым генер атором ТГ.

Выходы синхронизаторов 4 и 5 подключены ко входам бесконтактных переключателей, выполненных на логических ячейках б — 9, например «ИЛИ вЂ” НЕ». Разноименные

10 выходы двухпозиционн ых переключателей попарно логически запараллелены посредством ячеек 10 и 11 «ИЛИ вЂ” НЕ» и подключены к суммирующему 12 и вычитающему 1З входам блока 8.

15 Вторые выходы логических ячеек б — 9

«ИЛИ вЂ” НЕ», которые являются управляющими входами двухпозиционных переключателей, подключены к выходам триггеров 14 и 15, буфферных ячеек lб и 17 памяти. Вхо20 ды переноса ячеек lб и 17 подключены соответствен но ко входам синхронизаторов 4 и 5 блока 1.

Предлагаемый дискретный нуль-орган работает следующим образом.

25 Входные импульсы сергий задания и отработки поступают на входы синхронизаторов

4 и 5 в произвольной фазовой ориентации.

На выходах этих синхронизаторов импульсы появляются с некоторым запозданием в мо30 менты времени, соответствующие моментам

372541

55

65 времени появления сдвинутых импульсов тактового генератора.

Так как импульсы тактового генер атора, подаваемые на соответствующие входы синхронизаторов 4 и 5, сдвинуты по фазе следовани я на 180, импульсы задания и отработки, появляющиеся на выходах синхронизаторов, оказываются разнесенными во времени на величину, кратную половине периода частоты тактового генератора. Этим достигается безошибочный учет импульсов задания и отработки в блоке 8.

Допустим, что в и сходном состоянии напряжение на выходах синхронизаторов 4 и 5 соответствует напряжению логической единицы логических ячеек. Выходному импульсу соответствует исчезновение напряжения на выходах преобразователей, т. е, появление логического нуля. Логическая единица, поступающая с выхода синхронизатора 4 или с выхода синхронизатора 5 исключает логические единицы на выходах ячеек б, 7 или 8, 9 «ИЛИ вЂ” НЕ». При этом существуют логические еди|ницы на выходах ячеек 10 и 11

«ИЛИ вЂ” НЕ», подключенных ко входам 12 и

18 блока 8.

Если на выходе синхронизатора, например

4, появляется импульс, то на выходе ячейки

7 «ИЛИ вЂ” HE», на второй вход которой поступает логический нуль с выхода триггера

14, появляется логическая единица. Последняя исключает логическую единицу на выходе ячейки 10 «ИЛИ вЂ” НЕ», связанной с входом 12 блока. При этом в блоке 8 эапц сывается один импульс рассогласования со знаком «плюс». После появления импульса на входе синхронизатора 5 появляется импульс н а его выходе. Аналогично появляется логическая единица на выходе ячейки 9

«ИЛИ вЂ” НЕ», исключающая логическую едини1цу на выходе ячейки 11 «ИЛИ вЂ” НЕ», и на вход 18 блока 3 поступает импульс со знаком «минус», уменьшающий рассогласование на один импульс.

Инвертирование сигнала знаков задания и отработки может производиться в произвольный момент времени относительно периодов следовани я импульсов задания и отработки.

Пусть в некоторый момент времени знак задания и нвертируется на противоположный, B этот момент меняются местами логические нуль и единица на «входах 1 — знак». Однако триггер 14 пока остается в прежнем состоянии, так как блоки переноса 18 запрещают его опрокидывание, Первый импульс задания, поступающи и после смены знака на вход синхронизатора 4, запоминается в нем и, кроме того, воздействует на управляющие входы блоков переноса 18, являющиеся входом переноса буфферной ячейки памяти lб. В этот момент на входы триггера 14 поступают инвертированные логически и нуль и логическая единица и переводят триггер 14 в противоположное

4 состояние. Через некоторое время тактовый генератор б подвигает «записанный» в синхронизатор 4 импульс на выход, который с учетом нового состояния триггера 14 через логические ячейки б и 11 «ИЛИ вЂ” НЕ» «записывается» на вход 18 блока 3. Дальнейшими импульсами серйи задани я рассогласование в данном случае быстро уменьшается до нуля, а затем возрастает, определяя в следящей системе сигнаал рассогласования с противоположным знаком.

С некоторым запаздыванием относительно времени смены знака задания исполнительное звено следящей си стем1ы изменяет знак отработки;. При этом на «входах II — знак» происходит инвертирование логических нуля и единицы. Аналогично описанному первый импульс, поступающий на «вход II — частота», воздействуя на управляющие входы блоков переноса 19, обуславливает переход триггера 15 в противоположное состояние.

Появившись на выходе синхронизатора 5 с некоторым запозданием, данный импульс с учетом нового состояния триггера 15 через ячейки 8 и 10 «ИЛИ вЂ” НЕ» поступает н а вход 12 блока 8, уменьшая в нем число импульсов рассогласования.

Вследствие временной задержки прохождения импульса через синхр они заторы 4 и 5 попадание логических единиц на их выходах (на первых входах ячеек б и 7, а также, в равной степени, и на первых входах ячеек 8 и 9) происходит при состояниях триггеров 14 и 15, соответствующих знакам задания и отработки, существовавшим в моменты времен и поступления данных импульсов задания и отработки на входы синхронизаторов 4 и 5.

Следовательно, ориентированные по фазе импульсы задания и отработки, запаздывающие во времени, безошибочно коммутируются на суммирующий 12 (вычитающий) или вычитающий 18 (суммирующий) входы блока 3 в соответствии с истинными знаками задания и отработки.. Изменение знаков задания и отработки в течение времени задержки импульсов в синхронизаторах 4 и 5 благодаря ячейкам lб и 17, входы блоков переноса которых связаны со входами синхронизаторов, не может вызвать ложного переключения входов 12 и 18 блока 3, так как триггеры 14 m 15 находятся в прежнем состоянии до появления следующих входных импульсов, поступающих на входы синхронизаторов после учета предыдущих импульсов бло.ка 8.

Предмет изобретения

Дискретный нуль-орган, содержащий два входных синхронизатора, соединенных с тактовым генератором, выходы которых через блок коммутация импульсов соедияены со счетно-преобразовательным блоком, отличаюи ийся тем, что, с целью повышения точности работы устройства, оно содержит триггеры

372541 выходу этих триггеров, два входа которых через соответствующие блоки переноса подключены ко входам входных синхронизаторов.

Составитель Н. Мукосеева

Техред Т. Ускова

Редактор Л. Утехина

Корректор Т. Гревцова

Заказ 1357/2 Изд. № 285 Тираж 780 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4j5

Типография, пр. Сапунова, 2 и блоки переноса; причем первый и второй входы блока коммутации импульсов подключены к одному из выходов соответствующего триггера, третий и четвертый — к другому ф ь1