Устройство для моделирования задач теплопроводности

Иллюстрации

Показать всеРеферат

: 1т alllNRA бнблюсiтфещ е

373735

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №вЂ”

Заявлено 01.Х.1971 (М 1701300/18-24) с присоединением заявки ¹â€”

Приоритет—

Опубликовано 12Л11.1973. Бюллетень № 14

Дата опу.бликования описания 13Х1.1973

М,Кл. G Обд 7/56

Комитет оо делзм изобретений и открытий орн Совете Министров

СССР

УДК 681.333 (088.8) Авторы изобретения

И. А. Николаев, Л. К. Бабенко и P. H. Бабкина

Таганрогский радиотехнический институт

Заявитель

УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЗАДАЧ

ТЕПЛОПРОВОДНОСТИ

Изобретение относится к области вычислительной техники и может быть использовано при конструировании и разработке специализированных устройств, предназначенных для решения двумерного уравнения теплопроводности методом дискретизации пространства.

Известными специализированными устройствами, позволяющими решать уравнение теплопроводности методом дискретизации пространства, являются аналоговые г>ычислительные машины (ЛВМ) .

Однако эти устройства имеют существенный недостаток — низкую точность вычислений.

Устранение этого недостатка путем создания гибридных вычислительных систем связано с известными трудностями согласования двух форм представления информации. В связи с этим возникает необходимость построения специализированных устройств дискретного действия для решения дифференциальных уравнений в частных производных, в частности двумерного уравнения теплопроводности.

Целью изобретения является повышение точности решения двумерного уравнения теплопроводности методом полной дискретизации пространства по сравнению с точностью решения этого уравнения тем же методом на АВМ.

Эта цель достигается путем построения цифровой интегрирующей ячейки, предназначенной для интегрирования уравнения в точке (I, 1) полностью дискретизированного llpoстранства.

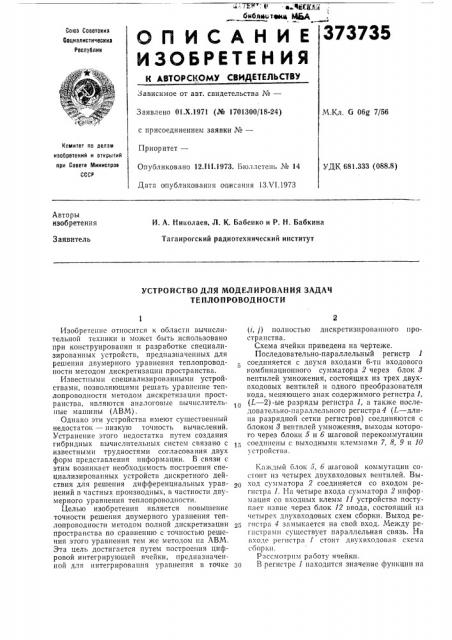

Схема ячейки приведена на чертеже.

Последовательно-параллельный регистр 1 соединяется с двумя входами 6-ти входового комбинационного сумматора 2 через блок 3 вентилей умножения, состоящих из трех двухвходовых вентилей и одного преобразователя кода, меняющего знак содержимого регистра 1, (L 2)-ые разряды регистра 1, а также последовательно-параллельного регистра 4 (L длина разрядной сетки регистров) соединяются с блоком 8 вентилей умножения, выходы которого через блоки 5 и б шаговой перекоммутации соединены с выходными клеммами 7, 8, 9 и 10 устройства.

Каждый блок 5, б шаговой коммутации состоит из четырех двухвходовых вентилей. Выход сумматора 2 соединяется со входом регистра 1. На четыре входа сумматора 2 информация со входных клемм 11 устройства поступает извне через блок 12 ввода, состоящий из четырех двухвходовых схем сборки. Выход регистра 4 замыкается на свой вход. Между регистрами существует параллельная связь. На входе регистра 1 стоит двухвходовая схема соорки.

Рассмотрим раооту ячейки. зп В регистре 1 находится значение функции на ф1

ИФ

373735

Составитель В. Тимохина

n+ — слое U"+ 2. процессе итераций это

2 значение уточняется до тех пор, пока не будет

n+ — n+— выполняться U +12 — U» (в, где в— точность решения. Количество итераций, необходимых для выполнения этого условия, счи1

n+— тается заданным. Точное значение U вы2 дается параллельно в регистр 4 по сигналу со входа И, где находится в течение времени, необходимого для вычисления функции на следующем полушаге со значением функции

Un . Граничные или начальные данные входа 13 заносятся в регистр 1 до начала вычислений.

Умножение содержимого регистров 1, 4 осуществляется путем съема информации с (L — 2) -ых разрядов регистров (L — длина разрядной сетки) с последующим выделением

L разрядов в блоке 8 вентилей умножения при помощи сигнала со входа 14.

Блоки 5 и 6 служат для перекоммутации выходов 7 — 10 устройства после окончания полушага интегрирования. Это связано с тем, что на четных и нечетных полушагах ячейки коммутируются между собой по-разному. Перекоммутация осуществляется путем подачи в первом полушаге сигнала со входа 15 на два вентиля блоков 5 и 6, шаговой коммутации, сигнала со входа 16 на два других вентиля блоков 5 и б во втором полушаге. При этом сигналы на входах 15 и 16 находятся в противофазе. Информация со входов 11, 17 поступает извне через блок ввода 12 на сумматор 2, где суммируется с информацией, идущей из

15 блока 8 вентилей умножения.

Предмет изобретения

Устройство для моделирования задач тепло20 проводности, содержащее блок ввода, соединенный с сумматором, и блок умножения, отличающееся тем, что, с целью повышения точности решения, оно содержит два последовательно-параллельных регистра, подсоединенных выходами к блокам умножения, и блоки шаговой коммутации, входы которых подключены к блоку умножения, соединенному с сумматором, выход которого соединен со входом одного из регистров.

1 едактор Б. Нанкина Техред Л. Грачева

Корректор Н. Аук

Лак l;l 251() Изд. _#_2 1291 Тираж 647 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий прп Совете Министров СССР

Москва, 7К-35, Раушская иаб., д. 4/5

Обл. тип. Костромского управления издательств, полиграфии и к11нжной торгов:и