Усилитель считывания

Иллюстрации

Показать всеРеферат

ОПИСАНИ Е

Саксо Сазатских

Социзлиститеских.Реслублин

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 0111.1971 (М 1623220/18-.24) с присоединением заявки ¹

Приоритет

Опубликовано 20.111.1973. Бюллетень № 15

М. Кл. G 11с 7/02

Комитет оо делам изобретений и открытий ори Совете Министров

СССР

УДК 681.327(088.8) Дата опубликования описания 4Л П.1973

Автор изобретения

В. А. Старовойтов

Заявитель

УСИЛИТЕЛЬ СЧИТЫВАНИЯ

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих запоминающих устройств (ЗУ) с большим уровнем помех.

Известные усилители считывания, предназначенные для усиления и выделения сигналов с двух сердечников при воздействии помехи от записи, содержат на входе два эмиттерных повторителя, нагруженных на согласованные волновые линии. Между первым и вторым дифференциальными каскадами усилителя включена линия задержки. Выходной каскад представляет собой бистабильную схему, выполненную на туннельном и полупроводниковом триодах.

Однако известные усилители работают только с однополярной помехой. Кроме того, в них используют широкополосную линию задержи (т. е. коаксиальный кабель), что при большом времени задержки (300 — 75 нсек) увеличивает размеры устройства. Помимо этого, при воздействии помехи от записи возможно насыщение транзисторов дифференциального усилителя, что увеличивает время восстановления рабочего режима и, следовательно, увеличивает рабочий цикл запоминающего устройства.

Цель изобретения — подавление двухполярной помехи при записи и повышение быстродействия усилителя считывания.

Для этого предлагаемый усилитель содержит токозадающие каскады; эмиттеры транзисторов двух токозадающих каскадов подключены к резисторам, общая точка которых

5 соединена с входной:клеммой устройства, коллекторы этих транзисторов соединены соответственно с эмиттерами транзисторов первого дифференциального каскада усиления.

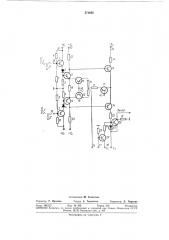

На чертеже изображена схема предлагае10 мого усилителя.

Первый каскад усилителя построен на двух эмиттерных повторителях, собранных на транзисторах 1 и 2, которые соединены с дифференциальным усилителем через диоды 3 и 4.

15 Нагрузкой эмиттерных повторителей служат резисторы 5 и б. Резисторы 7 и 8 согласуют выходное сопротивление разрядной линии с входом усилителя. Резисторы 9 и 10 задают режим транзисторов 1 и 2. Диоды 8 и 4 пре20 дотвращают пробой транзисторов 1 и 2 обратным напряжением. Второй каскад усилителя считывания собран по дифференциальной схеме на транзисторах 11 — 14, эмиттеры которых подключены к коллекторам токозадаю25 щих транзисторов 15, 1б и 17. Транзисторы

11 — 14 используются для усиления и выделения сигнала на фоне стробирующего импульса. Транзисторы 15, 1б и 17 служат источниками тока для транзисторов дифференциаль30 ного усилителя, стабилизируют усиление и за3 дают рабочий режим транзисторов 11 — 14 при стробировании. Резистор 18 создает низкоомную связь между эмиттерами тра«зисторов 11 и 12. Резисторы 19 и 20, подключенные к эмиттерам транзисторов 15 и lб, задают необходимый для дискриминации разбаланс эмиттерных токов токозадающих транзисторов 15 и lб, а также необходимый рабочий ток эмиттеров транзисторов 11 и 12 первой дифференциальной пары. Резистор 21, подключенный к эмиттеру транзистора 17, задает ток эмиттера транзистора 17, а также рабочий ток эмиттеров транзисторов 18 и 14 второй дифференциальной пары. Резисторы

22 — 25, подключенные к коллекторам транзисторов 11 — 14, являются коллекторными нагрузками этих транзисторов, Первый и второй дифференциальные каскады связаны непосредственной связью. Второй дифференциальный каскад соединен через нагрузочный резистор 25 с входом бистабильной схемы, построенной на транзисторе 2б и туннельном диоде 27.

Транзистор 28 используется для блокирования туннельного диода. Резистор 29, подключенный к базе транзистора 28, задает базовый ток этого транзистора. Резистор 80 задает ток блокировки туннельного диода. Резистор 81 является коллекторной нагрузкой транзистора 2б. К выходным клеммам 82 — 85 подключены источники питания E1 = 20 в, — Е = — 15 в, — Е = — 20 в, — Е4 — — — 25 в. С входной клеммой 8б соединен формирователь тактовых стробирующих импульсов, а с клеммой 87 — формирователь коротких стробирующих импульсов, осуществляющий временную селекцию сигнала считывания. Входной сигнал подается с клемм 88 и 89 на базы эмиттерных повторителей.

Устройство работает следующим образом.

Сигнал считывания «О» или «1» с дву.х сердечников поступает на вход усилителя считывания (клеммы 88 и 89) и выделяется на нагрузке эмиттеров (резисторы 5 и б) транзисторов 1 и 2, работающих в линейном режиме. К моменту прихода сигнала считывания дифференциальный усилитель, связанный с эмиттерными повторителями через диоды 8 и 4 непосредственной связью, подготовлен тактовым стробирующим импульсом. В данном усилителе применено стробирование двух дифференциальных каскадов, построенных «а транзисторах 11 — 14, по току, позволяющее получить малое время восстановления рабочего режима усилителя.

Дифференциальный каскад во время считывания совмещает две функции: усиление считанного сигнала «1» нли «0», выделение и дискриминацию по минимуму сигнала считан374656

5 lб. Получившаяся при этом разность потен45

40 ной «1». Дискриминация осуществляется изза разбаланса рабочих коллекторных токов транзисторов 11 и 12, который задают источники токов, собранные на транзисторах 15 и циалов на базах транзисторов 18 и 14 закрывает транзистор 14 выходного дифференциального каскада и открывает транзистор 18, При считывании «1» приходящий с эмиттерных повторителей сигнал усиливается первым дифференциальным каскадом на транзисторах 11 и 12 и выделяется на коллекторных резисторах 22 и 28. Коэффициент усиления первого каскада дифференциального усилителя токов показывает, что минимальный сигнал считанной «1», усиленный этим каскадом, превышает напряжение дискриминации. Транзистор 14 открывается и входит в режим усиления. Коллекторный ток этого транзистора возрастает. В коллекторную цепь транзистора 14 включена бистабильная схема на туннельном диоде 27 и транзисторе 2б. До прихода сигнала считывания бистабильная схема блокирована коллекторным током насыщенного транзистора 28. В требуемое время подается стробирующий импульс временной селекции, который запирает блокирующий транзистор 28. Ьистабильная схема срабатывает, и на выходе транзистора 2б выделяется сформированный сигнал считанной «1».

При считывании «О» сигнал также усиливается первым дифференциальным каскадом на транзисторах 11 и 12 и выделяется на коллекторных резисторах 22 и 28, Но поскольку сигнал считанного «О» имеет другую полярность, чем сигнал считанной «1», то напряжение, выделенное на резисторах 22, 28, суммируясь с напряжением дискриминации, еще больше запирает транзистор 14. Поэтому при считывании «О» сигнал на выходе бистабильной схемы отсутствует.

Предмет изобретения

Усилитель считывания, содержащий входные эмиттерные повторители, последовательно включенные дифференциальные каскады усиления и выходной бистабилы|ый каскад

«а туннельном диоде и транзисторе, отличаюи1ийся тем, что, с целью подавления двухполярной помехи при записи и повышения быстродействия усилителя, он содержит токозадающие каскады, эмиттеры транзисторов двух токозадающих каскадов подключены .к резисторам, общая точка которых соединена с входной клеммой устройства, коллекторы этих транзисторов соединены соответственно с эмиттерами транзисторов первого дифференциального каскада усиления.

374656 — C

Составитель Ю. Розенталь

Редактор Т. Иванова

Техред 3. Тараненко Корректор Л. Чуркина

Типография, пр. Сапунова, 2

Заказ 1843/15 Изд. № 359 Тираж 576 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5