Вс"осюзн.ая f>& fi/tpi^^vt ';," """у---л^ автор изобретения заявитель

Иллюстрации

Показать всеРеферат

377787

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сойа C011YOKHR

Социалистических

Республии

Зависимое от авт. свидетельства №вЂ”

Заявлено 28,IX,1970 (№ 1484680/18-24) с присоединением заявки №

Приоритет

Опубликовано 17.IV.1973. Бюллетень № 18

Дата опубликования описания 27Х1.1973

М. Кл. б 06f 15/34 помитет по делам изссретеиий и открытий при Совете Министров

СССР

УДК 681.3:519.2 (088.8) Автор изобретения

В. С. Гладкий

Морской гидрофизический институт АН Украинской ССР

Заявитель

ПРИСТАВКА К ЦИФРОВОИ ВЫЧИСЛИТЕЛЪНОй МАШИНЕ ДЛЯ

ЭКСПРЕСС-ОБРАБОТКИ ДАННЫХ

Изобретение относится к области вычислительной техники и может быть использовано, например, в качестве приставки к существующим типовым цифровым вычислительным .машинам (ЦВМ) («Минск-22», «М-220М» и др.) при вычислении основных характеристик случайных процессов (дисперсии, автокорреляционной функции) в реальном масштабе времени.

В настоящее время при вычислении на ЦВМ характеристик случайных процессов подавляющая часть машинного времени расходуется на промежуточные операции и вычисления, такие как сдвиг информации и получение попарных произведений из чисел исходного ряда. Это приводит к тому, что ЦВМ не в состоянии обработать входную информацию в реальном масштабе времени.

Цель изобретения состоит в устранении указанного недостатка.

Цель достигается тем, что в приставке входное устройство соединено с блоком динамической памяти, выходы блока управления, на который подаются синхроимпульсы, соединены с управляющими входами блока коммутации и блока динамической памяти, другие входы которого соединены с выходами блока коммутации, Выходы блока динамической памяти подключены ко входам вероятностных двоичных элементов, выходы которых через схему

«И» являются выходом приставки.

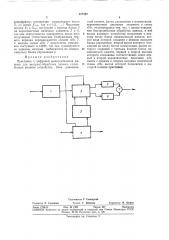

Блок-схема предлагаемого устройства приведена на чертеже.

5 Приставка содержит входное устройство 1, представляющее собой буферный регистр для приема исходных данных, блок 2 динамической памяти 1, представляющий собой m параллельно работающих регистров сдвига на

10 l тактов каждый, где 1 — число точек вычисляемой корреляционной функции, а т — разрядность числа на входе приставки, блок коммутации 8, управляющий блоком 2 для получения произведений пар чисел вида Х; Х,+, 15 где 1=1,2...., 1, блок управления 4, вероятностные двоичные элементы 5 и б, содержащие датчик случайных чисел и схемы сравнения, и логическую схему «И» 7.

Устройство работает следующим образом, 20 На входы приставки подаются числа Х; исходного ряда и синхроимпульсы. Числа Х; поступают через входное устройство 1 на блок динамической памяти параллельными т-разрядными кодами, которые продвигаются впра25 во на один разряд при поступлении импульса сдвига.

Синхроимпульсы осуществляют продвижение чисел по блоку 2 и одновременно поступают на блок управления, который через блок

30 коммутации, представляющий собой обычный

377787

Составитель Т. Солодухов

Техред Г. Дворина

Редактор Е. Семанова

Корректор И. Божко

Заказ 1730 13 Изд. Ко 1392 Тираж 647 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 дешифратор, поочередно коммутирует число

Х; со всеми Х;<л, где к=1,2,..., 1. Числовые потоки Х; и Х;+л поступают с выхода блока 2 на вероятностные двоичные элементы 5 и 6, где они статистически кодируются, после чего полученные статистические отображения первого порядка перемножаются схемой «И» 7.

С выхода схемы «И» 7 результаты умножения поступают в ЦВМ, где они суммируются по адресам, которые выбираются по синхроимпульсу блока управления 4.

Предмет изобретения

Приставка к цифровой вычислительной машине для экспресс-oolp300TKH данных, содержащая входное устройство, блок динамической памяти, блоки управления и коммутации, вероятностные двоичные элементы и схему

«И», отличающаяся тем, что, с целью повышения быстродействия обработки данных, в ней

5 выход входного устройства подключен к nept!oMy входу блока динамической памяти, второй вход которой соединен с первым выходом блока управления, второй выход которого подключен ко входу блока коммутации, выход ко10 торого соединен с третьим входом блока динамической памяти, первый и второй выходы которого соединены соответственно через первый и второй вероятностные двоичные элементы с первым и вторым входами логической

15 схемы «И», выход которой подключен к выходной клемме приставки.