Всесоюзная i те , y''"1*t'*''* *^-**'*^'l1'5t"'f^jf 4 ftf

Иллюстрации

Показать всеРеферат

О п И С А Н И Е 378805 изоьеитиния

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Саюо Советских

Социалистических

Реслублик

Зависимое от авт. свидетельства №вЂ”

Заявлено 12 1Ч.1971 (№ 1651996/18-24) с присоединением заявки №

Приоритет

Опубликовано 18.IV.1973. Бюллетень № 19

Дата опубликования описания 17ХП.1973

М. Кл. G 05Ь 19/18 йамнтет ао лолам изобретений и открытий

IlpN Совете Министров

СССР

УДК 681 335 87:621 9 .503.55 (088.8) Авторы изобретения

В. С. Шатунов, Г. Н. Кузьминых и Г. М. Набережнов

Заявитель

ИНТЕРПОЛЯТОР ДЛЯ ЦИФРОВОГО ПРОГРАММНОГО

УПРАВЛЕНИЯ

Изобретение относится к автоматическому управлению и предназначено для использования в системах программного управления группой объектов.

Известны интерполяторы для цифрового программного управления, содержащие последовательно соединенные устройство ввода данных, устройство буферной памяти, интерполирующее устройство и выходное устройство, а также устройство задания, скорости, соединенное с выходом устройства ввода данных, и устройство управления, выходы которого подключены к соответствующим входам устройств ввода данных, вывода и задания скорости, а вход — к соответствующим выходам интерполирующего устройства, Описываемый интерполятор отличается тем, что устройство буферной памяти содержит блок зон памяти и подключенный к нему |блок распределения информации; интерполирующее устройство выполнено в виде набора автономных однокоординатных блоков интерполяции, выходное устройство содержит коммутатор выходных каналов, соединенный с блоком распределения выходных импульсов, а устройства задания скорости состоит из блока задания, выходы которого подключены к блоку распределения скоростей, причем вход блока зон памяти подключен к выходу устройства ввода данных, выходы блока распределения информации подключены, к одним входам блоков интерполяции, к друтим входам которых, подключены выходы блока распределения скоростей, входы коммутатора выходных каналов соединены с соответствующими выходами блоков интерполяции, а вход блока задания подключен к выходу устройства ввода данных.

Это позволяет обеспечить одновременное управление группой объектов по разным программам.

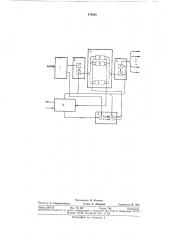

На чертеже показана функциональная схема описываемого интерполятора.

Схема содержит устройство 1 ввода дан15 ных, устройство 2 буферной памяти, интерполирующее устройство 8, выходное устройство 4, устройство 5 задания скорости, устройство б управления, блок 7 зон памяти, блок 8 распределения информации, однокоординат20 ные блоки 9 интерполяции, коммутатор 10 выходных каналов, блок 11 распределения выходных импульсов, блок 12 задания скорости и блок 13 распределения скоростей.

Исходная информация от управляющей

25 электронно-вычислительной машины (ЭВМ) по проводным каналам связи поступает на устройство 1, которое производит распределение этой информации по зонам памяти, Кро.ме того, из ЭВМ на устройство б поступает

30 команда, несущая информацию о принадлеж378805 нОсти каждой 30ны памяти конкретному объекту (станку) из группы. Блок б управления формирует команды для работы блока 8 распределения информации, блока 18 распределения скоростей и коммутатора. 10 выходных каналов. Команда работы блока 8 содержит адреса свободных интерполирующих блоков и адрес зоны, содержимое которой блок 8 пересылает в рабочие устройства свободных интерполирующих блоков и блока 12 задания скорости.

Команда работы блока. 18 -одержит адреса свободных интерполирующих блоков и адрес рабочего канала блока 12, который подключается к указанным интерполирующим блокам. Команда работы коммутатора 10 выходных каналов -содержит адреса интерполирующих блоков 9, адрес станка и адрес его координатной системы, к которой коммутатор 10 подключает .выход указанного в этой команде интерполируюшего блока. Таким образом, блок 8 распределения информации осуществляет выборку информации из блока 7 зон памяти и распределение ее по интерполирующим блокам 9 и рабочим устройствам блока 12 задания скорости. При этом коды перемещений по координатам отсылаются в интерполирующие блоки 9, а коды скоростей— в регистры блока 12 задания скоростей. Блок распределения скоростей производит подключение рабочих кан алов блока 12 к интерполирующим блокам 9, адреса которых указаны в команде работы блока 18 распределения скоростей.

Коммутатор 10 выходных каналов осуществ чяет подключение выходов интерполируюших блоков 9, адреса которых указаны в команде работы коммутатора, к координатным входам объектов (станков), адреса которых также указаны в этой команде.

После окончания заполн ения исходной информацией блоков 9 интерполирования и регистров блока 12 задания скорости и осуществления всех вышеуказанных подключений интерполирующие блоки производят отработку введенной в них информации. Во время этой

45 отработки блок 1 зон памяти заполняется новой ин формацией из ЭВМ. По окончании работы каждый интерполирующий блок выдает сигнал на устройство б управления, который формирует команду для заполнения их новой информацией. Так продолжается до тех пор, пока не отраоотаются полностью все программы всех объектов (станков), которые хранятся в накопителях управляющей ЭВМ, Предмет изобретения Интерполятор для цифрового программного управления, содержащий последовательно соединенные устройства ввода данных, устройство буферной памяти, интерполирующее устройство и выходное устройство, а также устройство задания скорости, соединенное с выходом устройства ввода данных, и устройство управления, выходы которого подключены к соответствующим входам устройств ввода данных, вывода и задания скорости, а вход— к соответствующим выходам интерполирующего устройства, отлачающийся тем, что, с целью одновременного управления группой объектов по разным программам, устройство буферной памяти содержит блок зон памяти и подключенный к нему блок распределения информации; интерполирующее устройство выполнено в виде набора автономных однокоординатных блоков интерполяции, выходное устройство содержит коммутатор .выходных каналов, соединенный с блоком распределения выходных импульсов, а устройство задания скорости состоит из блока задания, выходы которого подключены к блоку распределен ия скоростей, причем вход блока зон памяти подключен к выходу устройства ввода данных, выходы блока распределения информа ции подключены к одним входам блоков интерполяции, к другим входам которых подключены выходы блока распределения скоростей, входы коммутатора выходных каналов соединены с соответствующими выходами блоков интерполяции, а вход блока зада,ния подключен к выходу устройства ввода д,ан1ных.

378805

Составитель В. Казаков

Редактор 3. Твердохлебова Техред Г. Дворина Корректор Н. Аук

Заказ 1976/15 Изд. № 460 Тираж 780 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2