Патент ссср 378851

Иллюстрации

Показать всеРеферат

378851 б П Й СА Н Й Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства Хе

М. Кл. G 06f 11. 00

G 06f 3/00

Заявлено 07.Ill.1969 (№ 1323478/18-24) с присоединением заявки К

Приор итет

Опубликовано 18ЛЧ.1973. Бюллетень М 19

Дата опубликования описания 11.VII.1973

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 681.326.7(088.8) Авторы изобретения

P. А. Варламов и А. Н. Чистяков

Заявитель

УСТРОЙСТВО ВВОДА — ВЫВОДА СО СХЕМНЪ|М КОНТРОЛЕМ

Изобретение относится к области вычислительной техники и предназначено для использования в информационно-управляющих системах с ЦВМ.

Информационно-управляющие системы оперируют большими потоками входной и выходной информации, Сбор, распределение и преобразование информации выполняется с помощью устройств ввода — вывода (УВВ).

С целью повышения надежности системы входящие в ее состав приборы охватываются автоматическим контролем исправности, а в системах с малым временем восстановления— также автоматическим поиском места неисправности.

Известны цифровые устройства, охваченные автоматическим программно-схемным контролем и программным поиском места неисправности.

В подобных устройствах могут быть использованы узлы с автономными схемами контроля исправности.

Однако при применении схемно-программного контроля к устройствам ввода — вывода наряду с такими общими недостатками, как возможность возникновения неисправности в периоды между выполнениями контрольных программ, затраты машинного времени и команд ДЗУ на контрольные программы, выявляется дополнительное ограничение к его применению: при контроле выходных исполнительных элементов происходит выдача во внешние устройства ложных исполнительных сигналов.

С целью повышения эффективности контроля и поиска места неисправности и более полного охвата контролем оборудования устройства, включая аппаратуру контроля, предлагается устройство ввода — вывода со схем10 ным контролем, содержащее регистр контроля, который позволяет формировать сигнал исправности устройства в целом и фиксировать место неисправности, включая сам регистр контроля.

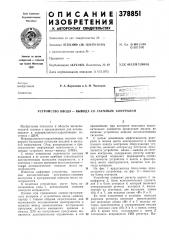

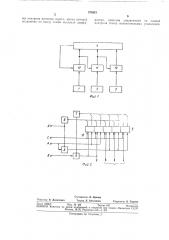

15 На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 — блок-схема блока контроля.

Устройство содержит регистр адреса 1, дешифратор 2, блок исполнительных усилите20 лей 8 и блок контроля 4, который включает пятиразрядный регистр контроля 5, выполненный на триггерах, две выходные схемы

«И» б и 7; две входные схемы «И» 8 и 9.

Ко всем единичным и нулевым выходам

25 разрядов регистра контроля присоединены две выходные схемы «И» б и 7, выходы которых присоединены к управляющим входам двух входных схем «И» 8 и 9, а выход схемы

«И» б, кроме того, подсоединен к шине Л

30 потенциала исправности УВВ регистра. Вы378851

65 ход первой схемы «И» 8 подключен к нулевым входам всех разрядов регистра, за исключением двух первых, а выход второй

9 — к единичным входам двух первых разрядов и ко входу схемы контроля регистра адреса 10, выход которой подключен к единичному входу 3-ro разряда регистра и ко входу схемы контроля дешифратора 11. Выход схемы контроля дешифратора подключен к единичному входу 4-го разряда регистра и ко входам схемы контроля блока исполнительных усилителей 12, ьыход которой подключен к единичному входу 5-го разряда регистра, кроме того, к единичным входам всех разрядов подключены также шина установки в единичное состояние 18.

Операция ввода — вывода выполняется спомощью тактовых импульсов А, В и С, вырабатываемых ЭЦВМ, эти же импульсы используются и для целей контроля. Шина первого тактового импульса А подключена к нулевым входам двух первых разрядов регистра контроля и к первой входной схеме «И».

Шина второго тактового импульса В подключена ко второй входной схеме «И»; шипа импульса окончания операции С вЂ” к единичным входам разрядов регистра контроля.

К началу выполнения операции регистр контроля 5 находится в единичном состоянии в результате выполнения предыдущей операции.

Первый тактовый импульс А производит запись адреса на регистр адреса 1, устанавливает в состояние «00» два первых разряда регистра контроля 5, опрашивает первую входную схему «И» 8 и через нее устанавливает в нулевое состояние остальные разряды регистра.

Второй тактовый импульс В опрашивает вторую входную схему «И» 9 и по нулевому состоянию регистра проходит через нее на установку в состояние «11» двух первых разрядов регистра и на регистр адреса 1, дешифратор 2, блок исполнительных усилителей 8 в качестве исполнительного импульса и импульса опроса их схем автономного контроля.

Сигналы исправности, вырабатываемые этими схемами при условии исправности узлов, устанавливают все разряды регистра контроля в единичное состояние. На выходе схемы «И» б возникает сигнал «УВВ исправно», разрешающий ЦВМ закончить операцию ввода — вывода. По окончании любой операции (в том числе и операции, не относящейся к

«вводу — выводу») ЦВМ вырабатывает импульс С, который устанавливает триггеры регистра контроля в единичное состояние.

При неисправности контролируемых узлов или регистра контроля сигнал «УВВ исправно» не вырабатывается и производится автоматическое повторение операции, начииая с им пул ьс а С.

При неисправности контролируемого узла сигнал исправности со схемы автономного контроля этого узла ие выдается и соответствующий разряд регистра контроля в единичное состояние ие устаиавлиьается. Сигнал

«УВВ исправно» при этом ие формируется и дальнейшее выполнение блокируется. На регистре контроля 5 фиксируется код, соответствующий месту неисправности, два первых разряда находятся в состоянии «11».

При неисправности регистра контроля, состоящей в том, что разряд ие устанавливается в нулевое состояние, второй тактовый импульс В через вторую входную схему «И» ие проходит и сигнал «УВВ исправно» ие вырабатывается.

При этом на двух первых разрядах регистра фиксируется код «00», «01» или «10».

При неисправности регистра контроля, состоящей в том, что разряд ие устанавливается в единичное состояние, сигнал «УВВ исправно» не может быть сформирован, несмотря на наличие импульсов исправности от схем автономного контроля узлов. При повторении операции тактовый импульс С также не устанавливает неисправный разряд в

«1» состояние. Первый тактовый импульс А устанавливает два первых разряда в состояние «00», ио на установку остальных разрядов в нулевое состояние ие проходит. Прохождение второго тактового импульса блокируется и выполнение операций прекращается. Таким образом, любой неисправности регистра контроля соответствует наличие хотя бы одного нулевого состояния в двух первых разрядах регистра контроля.

Предмет изо бретения

Устройство ввода — вывода со схемным контролем, содержащее регистр адреса, дешифратор и блок исполнительных усилителей, подключенные соответственно через схему контроля регистра адреса, схему контроля дешифратора и схему контроля блока исполнительных усилителей к блоку контроля, состоящему из регистра контроля, к единичным входам триггеров которого подсоедииеиа шина установки в единичное состояние, двух выходных схем «И», входы которых связаны соответственно с единичными и пулевыми выходами триггеров, а выходы — с соответствующими входами первой и второй входных схем «И», отличающееся тем, что, с целью повышения надежности работы устройства, регистр контроля содержит два дополнительных триггера, нулевые входы которых и второй вход первой входной схемы

«И» подключен к шине первого тактового импульса, а выход первой входной схемы

«И» соединен с нулевыми входами остальных триггеров регистра контроля; ко второму входу второй входной схемы «И» подключена шина второго тактового импульса, а выход второй входной схемы «И» подсоединен к единичным входам двух дополнительных триггеров регистра контроля и ко входу схе378851

Составитель В. Орлова

Техред Л. Богданова

Редактор Н. Данилович

Корректор О. Тюрина

Заказ 1883/2 Изд. № 436 Тираж 647 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 3(-35, Раушская наб., д. 4/5

Типография, пр. Сапупова, 2 мы контроля регистра адреса, выход которой подключен ко входу схемы контроля дешифратора, выходом соединенной со схемой контроля блока исполнительных усилителей.