Юзнав

Иллюстрации

Показать всеРеферат

ОГ1ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союа Соеетскит

Сониалистическив

Республин

Зависимое от авт. свидетельства №

Заявлено 18.XII.1970 (№ 1604605/18-24) М. Кл. G 08с 25/00 с присоединением заявки №

Приоритет йомитет по делам изобретений и открытиЯ при Совете Министров

СССР

УДК 621.i398 (088.8) Опубликовано 18ЛЧ.1973. Бюллетень № 19

Дата опубликования описания 20Х1.1973.-:„..;.,:,.!ОЗНАГ

Л. В. Головинский, В. Х. Местечкин и Л. М. Смеркло

,и hАвторы изобретения

Заявитель

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК

ДЕКОДИРОВАННОЙ ИНФОРМАЦИИ

Изобретение относится к области телемеханики.

Известны устройства для обнаружения ошибок декодированной информации, содержащие дешифратор, схему совпадения и формирования управляющего сигнала ошибки, триггеры, эмиттерные повторители, усилителиинверторы и блок преобразования и записи информации.

Целью изобретения является упрощение устройства и повышение его надежности в работе.

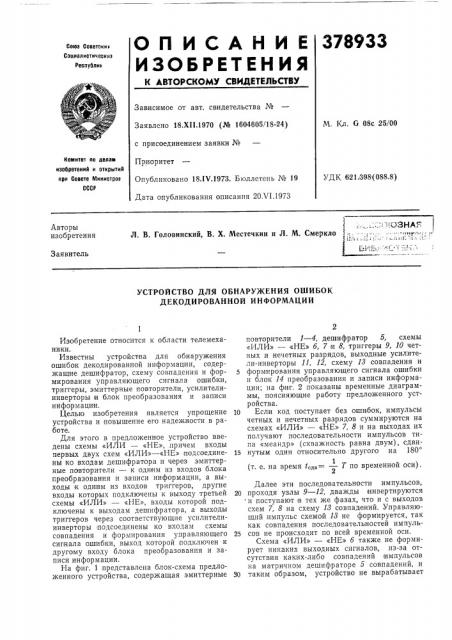

Для этого в предложенное устройство введены схемы «ИЛИ вЂ” «НЕ»,,причем входы первых двух схем «ИЛИ» — «HE»,ïîäñîåäèíåны ко входам дешифратора и через эмиттерные повторители — к одним из входов блока преобразования и записи информации, а выходы к одним из входов триггеров, другие входы которых подключены к выходу третьей схемы «ИЛИ» — «НЕ», входы которой подключены к выходам дешифратора, а выходы триггеров через соответствующие усилителиинверторы подсоединены ко входам схемы совпадения и формирования управляющего сигнала ошибки, выход которой подключен к другому входу блока преобразования и записи информации.

На фиг. 1 представлена блок-схема предложенного устройства, содержащая эмиттерные

2 повторители 1 — 4, дешифратор 5, схемы

«ИЛИ» — «НЕ» б, 7 и 8, триггеры 9, 10 четных и нечетных разрядов, выходные усилители-инверторы 11, 12, схему 13 совпадения и

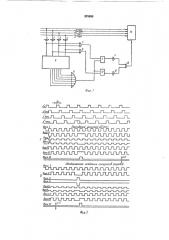

5 формирования управляющего сигнала ошибки и блок 14 преобразования и записи информации; на фиг, 2 показаны временные диаграммы, поясняющие работу предложенного устройства.

1о Если код поступает без ошибок, импульсы четных и нечетных разрядов суммируются на схемах «ИЛИ» — «НЕ» 7, 8 и на выходах их получают последовательности импульсов типа «меандр» (скважность равна двум), сдви15 нутым один относительно другого на 180

1 (т. е. на время 4л,= — Т по временной оси).

Далее эти последовательности импульсов, 20 проходя узлы 9 — 12, дважды стнвертируются и поступают в тех же фазах, что и с выходов схем 7, 8 на схему 18 совпадений. Управляющий импульс схемой 18 не формируется, так как совпадения последовательностей импуль25 сов не происходит по всей временной оси.

Схема «ИЛИ» — «HE» б также не формирует никаких выходных сигналов, из-за отсутствия каких-либо совпадений кмпульсов на матричном дешифраторе 5 совпадений, и

ЗО таким образом, устройство не вырабатывает

37893i3 1упр — акт управляющих сигналов и не влияет на работу блока 14 преобразования и записи информации.

Рассмотрим работу устройства при наличии в коде ошибок следующих типов: пропадание импульсов одного или нескольких разрядов, одновременное появление импульсов на двух и более сигнальных шинах.

В случае пропадания импульса (или импульсов) одного разряда, например «нулей» четных (см. фиг. 2 а), импульсы нечетных разрядов с выходов эмиттерных повторителей

1 и 8 (см. фиг. 1) поступают на схемы

«ИЛИ» — «НЕ» 7, а импульсы «единиц» четных разрядов выхода эмиттерного повторителя 4 поступают на схему «ИЛИ» — «НЕ» 8.

Таким образом, на выходе схемы 7 получают последовательность импульсов типа «меандр» а на выходе схемы 8 — отрицательные импульсы, соответствующие входным импульсам оставшихся четных «единиц». Эти импульсы дифференцируются и своими фронтами перебрасывают триггеры 9 и 10.

Перепады напряжения на выходе триггеров

9 и 10 управляют работой выходных усилителей инверторов 11 и 12, и,на выходе последних усилителей инверторов 11 и 12, и на выходе последних получают последовательности импульсов, показанные на фиг. 2а.

С помощью схемы И совпадения на выходе устройства получают управляющий импульс, сигнализирующий о наличии ошибки в коде, по длительности равный длительности импульса «пропавшего» разряда, т. е.

tlf р= tp. где 4,-,р — длительность импульсов управления, р длительность импульса одного разряда, с амплитудой где У,,,р — амплитуда импульса управления, U„— максимальная амплитуда напряжения на .выходе схемы «НЕ» блока 11, ЛУ вЂ” начальное смещение схемы «И».

При одновременном появлении импульсов на двух сигнальных шинах (например импульсов «единиц» четных и «нулей» нечетных) они повторяются на эмиттерных повторителях

1 (см. фиг. 2б) и одновременно воздействуют на схемы «ИЛИ» — «НЕ» 7, 8 и на дешифратор б (логическую диодную матр ицу сочетаний С4 ). Импульсы четных и нечетных разрядов, проходя схемы «ИЛИ» — «НЕ» 7, 8

20 г5

З5

55 устанавливают триггеры 9 и 10 в такое состояние, при котором в дальнейшем совпадение положительных импульсов невозможно.

Однако на одном из выходов дешифратора появляется положительный импульс, как результат совпадения импульсов «нулей» нечетных и «единиц» четных, который усиливается и инвертируется схемой «ИЛИ» — «HE» б.

Отрицательный импульс, снимаемый с выхода блока б, дифференцируется и своими фронтами управляет состоянием триггеров 9 и 10.

Состояние триггера 9 не изменяется, а лишь подтверждается, так как его выходные импульсы представляют собой «меандр» с периодом Т=21р. Триггер 10, который находился в состоянии высокого напряжения, не изменяет своего состояния под воздействием переднего отрицательного фронта (последний подтверждает его состояние) и перебрасывается в состояние низкого напряжения под воздействием заднего положительного фронта дифференцированного импульса.

Таким образом, н а выходе триггера 10 получают «меандр» с периодом следования

T=4tð, а на выходе схему 18 — управляющий импульс длительностью t, начинающийся по заднему фронту совпавших импульсов

«нулей» нечетных и «единиц» четных.

В дальнейшем управляющие импульсы используются в блоке 14 для сброса (срирания) записанной информации, в которой имеются ошибки (сбои), а также счета самих ошибок, Предмет изобретения

Устройство для обнаружения ошибок декодированной информации, содержащее дешифратор, схему совпадения и формирования управляющего сигнала ошибки, триггеры, эмиттерные повторители, усилители-инверторы и блок преобразования и записи информации, отличающееся тем, что, с целью упрощения устройства и повышения его надежности в работе, введены схемы «ИЛИ» — «НЕ», причем входы первых двух схем «ИЛИ» — «НЕ» подсоединены ко входам дешифратора и через эмиттерные повторители — к одним из входов блока преобразования и записи информации, а выходы к одним из входов триггеров, другие входы которых подключены к выходу третьей схемы «ИЛИ» — «НЕ», входы которой подключены к выходам дешифратора, а выходы триггеров через соответствующие усилители-инверторы подсоединены ко входам схемы совпадения и формирования управляющего сигнала ошибки, выход которой подключен к другому входу блока преобразования и записи информации.

378933

„Оче дык11 двий

„1 неч. ф! чеи.

Bmx. 7 дыхд ддИ . У

Вмх. 10 дих1Я

Вью. П джхд дых. 5

ых. б

Юых.У ею дих. jI

У3

Пропа8аний иип пьса Ячея) Однооременное поеоление импульсо1 разрядами