Способ изготовления пленочных микросхем

Иллюстрации

Показать всеРеферат

О И Е 38I31

Союз Советскии

Социалистических

Республик

К3ОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства ¹

Заявлено 04.1.1972 (№ 1733828/26-9) с присоединением заявки №

Приоритет

Опубликовано 15.11.1974. Бюллетень № 6

Дата опубликования описания 28Х1.1974

М. Кл. Н 051< 3/02

Гасударственный комитет

Совета Министров СССР аа делам изобретений и открытий

УДК 621.3.049.75(088.8) Авторы изобретения

Ю. А. Шепрут и Ю. А. Смирнов

Заявитель

СПОСОБ ИЗГОТОВЛЕНИЯ ПЛЕНОЧНЫХ МИКРОСХЕМ

Известен способ изготовления пленочных микросхем фотолитографическим методом, включающий нанесение на поверхность подложки сплошного слоя вентильного материала и его локальное анодирование.

Цель изобретения — упрощение технологии изготовления и повышение эксплуатационной надежности микросхем.

По предлагаемому способу в сплошном слое вентильного металла создают сквозные окна, обнажающие торцовые участки элементов схемы, подлежащие анодированию, а после локального анодирования наносят сплошной слой токопроводящего материала и выполняют полный коммутационный рисунок микросхемы на обоих токопроводящих слоях с учетом ранее полученного рисунка.

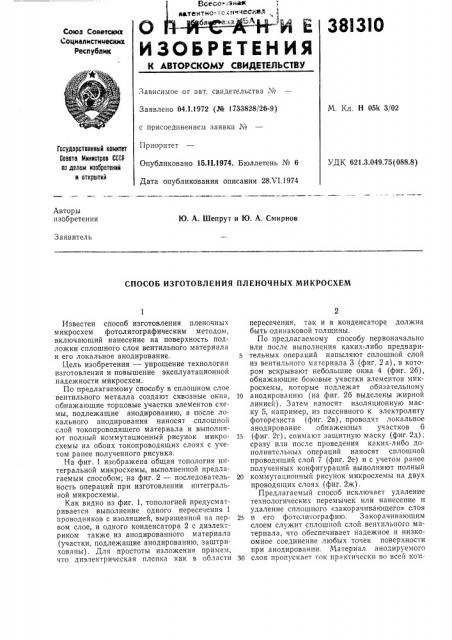

На фиг. 1 изображена общая топология интегральной микросхемы, выполненной предлагаемым способом; на фиг. 2 — последовательность операций при изготовлении интегральной микросхемы.

Как видно из фиг. 1, топологией предусматривается выполнение одного пересечения 1 проводников с изоляцией, выращенной на первом слое, и одного конденсатора 2 с диэлектриком также из анодированного материала (участки, подлежащие анодированию, заштрихованы) . Для простоты изложения примем, что диэлектрическая пленка как в области пересечения, так и в конденсаторе должна быть одинаковой толщины.

По предлагаемому способу первоначально или после выполнения каких-либо предварительных операций напыляют сплошной слой из вентильного материала 3 (фиг. 2 а), в котором вскрывают небольшие окна 4 (фиг. 2б), обнажающие боковые участки элементов микросхемы, которые подлежат обязательному

10 анодированию (на фиг. 2б выделены жирной линией). Затем наносят изоляционную маску 5, например, из пассивного к электролиту фоторезиста (фиг. 2в), проводят локальное анодирование обнаженных участков 6

lв (фиг. 2г), снимают защитную маску (фиг.2д); сразу или после проведения каких-либо дополнительных операций наносят сплошной проводящий слой 7 (фиг. 2е) и с учетом ранее полученных конфигураций выполняют полный

20 коммутационный рисунок микросхемы на двух проводящих слоях (фиг. 2ж).

Предлагаемый способ исключает удаление технологических перемычек или нанесение и удаление сплошного «закорачивающего» слоя

25 и его фотолитографию. Закорачивающим слоем служит сплошной слой вентпльного материала, что обеспечивает надежное и низкоомное соединение любых точек поверхности при анодировании. Материал анодируемого

30 слоя пропускает ток практически во всей ком381310

Составитель Е. Ковалева

Техред T. Ускова

Корректор М. Лейзерман

Редактор Б. Федотов

Заказ 1371,5 Изд. ¹ 1267 Тираж 760 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4,, 5

Типография, пр. Сапунова, 2 мутирующей части с <емы, что приводит к уменьшению сопротнвлс ня проводников, к повышению процеп га выхода годных схем б IiiI o IH > я p) блирова ни1о o IIo+o проводника другим и, в итоге, к повышепи,о эксплуатационной надежности мHHpoc;Ie;I.

Предмет изобретения

Способ изготовления пленоч11ых микросхем фотолитографическиAI ме годом, включа|ощий нанесение на поверхность подложки сплошного слоя вентильного материала и его локаль— пое анодирование, отличающийся тем, что, с целью упрсшения технологии изготовления и повышения эксплуатационной надежности микросхем, в сплошном слое вентильного металла созда1от сквозные окна, обнажаюц1ие торцовые уч":ñ:::è элементов схемы, подлежащие анодированию, а после локального аподирования наносят сплошной слой токопроводящего материала и выполняют полньш

10 коммутационный рисунок микросхемы на обоих токопроводящих слоях с учетом ранее получеш1ого рисунка.