Фазовый детектор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

М. Кл. Н 03а 3 00

Заявлено 16.XI.1971 (№ 1714701(26-9) с присоединением заявки №

Приоритет

Опубликовано 05.VII.1973. Ьюллстець ¹ 29

Дата опубликования описания ЗО.Х.1973

Государственный комитет

Совета Министров СССР оо делам изооретений и открытий

УДК 621.376.43 (088.8) Авторы изобретения

А. А. Лопатин и В. А. Мелькумов

Заявитель

ФАЗОВЫЙ ДЕТЕКТОР

Изобретение относится к рад1тотехнике.

Устройство может быть использовано при проектировании следящих систем.

Известны фазовые детекторы, состоящие из коммутирующего устройства и фильтра низких частот.

Наличие фильтра низких частот ухудшает динамические характеристики фазового детектора.

Цель изобретения — уменьшение постоянной времени детектора при одновременном сии>кении пульсаций выходного напряжения.

Достигается она тем, что в предлагаемый фазовый детектор дополнительно введен интегрирующий усилитель, вход которого соединен с источником входного сигнала, а выход зашунтирован последовательно соединенными конденсатором и ключом первой пары, причем их обгцая точка соединена со входом эмиттерного повторителя.

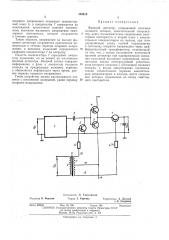

Схема устройства приведена на чертеже.

К выходу интегрирующего усилителя 1 подключены последовательно соединенные накопительный конденсатор 2 и транзисторный ключ 8. Общая точка конденсатора и транзисторного ключа соединена со входом эмиттерного повторителя на транзисторах 4 и 5.

Коллектор транзистора 4 подключен к минусу источника питания, а коллектор транзистора 5 — плюсу. Эмиттеры транзисторов соединены и через управляемый транзисторный ключ б подключены к одному из выводов накопительного конденсатора 7. Второй вывод конденсатора 7 соединен с общей точкой схемы. Выходное напряжение снимается с конденсатора 7. Транзисторные ключи 8 и б управляются опорным напряжением, имеющим вид знакочередующихся разнополярных импульсов большой cKBB?KIIocTH, от импульсного трансформатора 8. На первичную обмотку 9 подается опорное напряжение. Выход 10 вторичной обмотки 11 через резистор 12 соединен с базой транзистора ключа 8. Вывод 18 через резистор 14 соединен с базой транзисторного ключа б. Средний вывод 15 обмотки 11 соединен с коллектором транзистора 5.

Коротким отрицательным импульсом опорного напряжения открывается транзисторный ключ 8, и накопительный конденсатор заряжается до мгновенного значения выходного напряжения интегрирующего усилителя. По окончании импульса ключ 8 запирается, и напря:кение на конденсаторе 2 сохраняется неизменным в течение периода опорного напря>кения, а напряжение на входе эмиттер25 ного повторителя, а также на его выходе равно разности выходного напряжения интегрирующего усилителя и мгновенного значения этого >ке напряжения, соответствующего моменту действия отрицательного импульса

30 опорного напря>кения, Через полпериода положительный импульс

38961 0

Предмет изобретения

Составитель Л. Галактионов

Техрсд Т. Курилко

Редактор В. Федотов

Корректоры: Л. Дзесова и Е. Сапунов»

Заказ 282б/5 Изд. № 788 Тираж 780

ЦНИИПИ Государственного комитета Совета Министров СССР

l1o делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2 опорного напряжения открывает транзисторный ключ 6, и конденсатор 7 заряжается до напряжения, практически равного мгновенному значению выходного напряжения эмиттерного повторителя, которое сохраняется в течение периода.

Таким образом, напряжение на выходе фазового детектора сохраняется практически неизменным в течение периода опорного напряжения, а величина пульсаций определяется разрядом конденсатора 7 на нагрузку.

Емкость конденсатора 7 определяет амплитуду пульсации, но пе влияет на постоянную времени детектора. Входной сигнал содержит информацию о фазе и амплитуде входного 15 сигнала за предыдущую половину периода, а обновляется информация через время, равное периоду опорного напряжения.

Такое устройство можно рассматривать как звено с постоянной задержкой, равно периоду опорного напряжения.

Фазовый детектор, содержащий источник входного сигнала, накопительный конденсатор, ключ, последовательно соединенные эмиттерный повторитель и второй ключ с накопительным конденсатором на выходе, при этом управляющие входы ключей подсоединены к источнику опорного напряжения через дифференциальный трансформатор, отличагощийся тем, что, с целью уменьшения постоянной времени детектора при одновременном снижении пульсаций выходного напряжения, дополнительно введен интегрирующий усилитель, вход которого соединен с источником входного сигнала, а выход зашунтирован последовательно соединенными первыми накопительным конденсатором и ключом, место соединения которых подключено ко входу эмиттерного повторителя,