Устройство для фильтрации сигналов

Иллюстрации

Показать всеРеферат

союз советских I Q П И С А Н И

Социалистимеских

Республик

ИЗОБРЕТЕНИЯ

Зависимое от авт. свидетельства №

Заявлено 26ЛЧ.1971 (№ 1649170/18-24) М. Кл. Н 04b 7116 с присоединением заявки №вЂ”

Приоритет

Государственный комитет

Совета Министров СССР ла делам изааретаний и OTKpblTHH

Опубликовано 05Л 1!.1973. Бюллетень № 29

Дата опубликования описания 29.Х.1973

УДК 621.372,54 (088.8) Авторы изобретения В. К. Слока, В. Ф. Стручев, Д. В. Щелкин и В. И. Щетинин

Заявитель

УСТРОЙСТВО ДЛЯ ФИЛЬТРАЦИИ СИГНА

Изобретение от носится к радиотехнике.

Известны устройства для фильтрации сигналов, содержащие генератор опорного сигнала, к которому через фазорасщепитель подсоединены два сдвигающих регистра, матрицы весовых сумматоров и квадратичный сумматор. На выходе известных устройств фильтрации отношение сигнал — шум у мвньшается, что затрудняет выделение полезааого сигнала и изменение его параметров.

П|редложенное устройс PBQ отличается тем, "Iòo оно содержит два логических преобразователя, входы которых соединены с выходами фазовых детекторов, а выходы подключса|ы ко входам соответствующих регистров сдвига.

Каждый логический преобразователь содержит четыре схемы совпадения, два сумматора, два вычитателя, выходной сумматор и п оследовательно включенные многоу ровневый квантователь амплитуды и сдвигающий рс|истр, Bûõîäû которого попарно соединены со входами двух сумматоров и двух вычитателей, под ключенных через четыре схемы совпадения ко вх одам выходного сумматора. Это поз воляет повысить на выходе фильтра отношение полезного сигнала к фазоманипулировгHIIoй помехе.

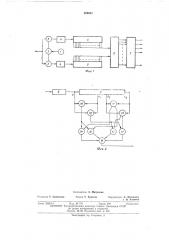

На фиг. 1 изобра кена блок-схема устройства.

Устройство состоит из генератора опорного си гнала 1, фазорасщепителя 2, двух квадратур ных каналов, вклк чаю щих в себя фазовые детекторы 8, логические преобразова5 тели 4, сдвигающие регистры с отводами 5, матрицы б и 7 весовых сумматоров и квадратичных сумматоров.

На фиг. 2 показана структурная схема логического преобразователя. Преобразователь

10 состоит из MIHol oуровневого квантователя 8, сдвигающе о регистра 9 с отвода ми на малое в сравнении с длительностью сигнала время, сумматоров 10, 11, вычита телей 12, 18, схем совпадения 14 — 17 и сумматора 18.

15 Элементы устройства соединены следующим образом.

Выход генератора опорного сигнала 1 соединен с фазорасщепителем 2, выход фазорасщепнтеля — с управляющими, входами

20 фазовых детекторов 8. Другие входы фазовых детекторов являются входом устройства.

Выходы фазовых дстекторов соединены с логическими преобразователями, выходы которых соединены со сдвигающимп регпстр а25 мп 5. К выходам сдвигающих регистров 5 подсоединс ны вх оды матрицы б весо вых су|мматоров, к выходам которой подсоединены входы матрицы 7 квадратичных сум маторов.

Входом логического преобразователя 4 явЗ0 ляется вход многоуровневого, квантователя

389631

8, выходы которого соединены с входами сдвнгающепо ре гистра 9, немеющего выходы с ОЙ, nI u, nzЙ, nqЙ позициЙ. Выходы ОЙ и

nJ-й позиций сдвигающего регистра соединены со входами, сумматора 10 и вычитателя

12, а выходы п.-й и п - é позиций — со входами сум матора 11 и вычитателя 18, имеющих

IipHIMbIc и инверсные выходы. Выходы сумматоров и вычитателей соединены со входами схем сов падения 14 — 17, причем прямые выходы сумматоров 10 и 11 прямо соедине; ны со входами схемы совпадения 14, прямой выход сумматора 10 и и нве рсный выход сумматора 11 — со входами схемы совпадения 15, прям ые выходы вычитателей 12 и

18 — со входами схемы совпадения 16 и, наконец, прямой выход вычитателя 12 и инверсный выход вычитателя 18 — со входами .схемы совпадения 17. Выходы схем совпаде,ния соеди неиы со входа ми сумматора 18, вы.ход которого. является выходом логического преобразователя 4.

Работает устрой ство следующи м образом.

Сипнал с выхода фазового детектора 8 поступает на вход многоуровневого ква нто ва- 25 теля 8, который квантует его по амплитуде, и дискретизирует по в реме ни,. На выходе многоуров йевого квантователя в. дискретные моменты времени имеются таким образом сигналы, преобразованные в цифровой код, т. е. коды.

Эти коды. поступают в сдвигающий регистр

9, который является многоканальным (IIIo числу разрядов кода входного сипнала), имеющим отводы от О-й, п1-й, п2-й, п -й по- 35 зиций сдвига. Величины nI, n2, ns определяются видом фазовой ма нипуляции помехи.

С отводов сигналы в виде кодов поступают на входы сумматоров и вычитателей, причем в сумматоре 10 произ водится сложение. ко- 40 дов с О-го и и>- го отводов, в сумматоре 11— сложение кодов с n2 iro и пз-го отводов, в вычитателе 12 код с п1-го отвода вычитается из,кода с О-го отвода, а в вы читателе 18 код с nq-Io отвода вычитается из кода с п2-го от- 45 вода. С вых одов сум)маторов и вычитателей сигналы в виде кодов поступают на входы схем совпадения, которые работают следующим образом.

На вых оде схемы совпадения 14 появится 50 сигнал, соответствующий логической единице, если код с прямого выхода сумматора 10 больше кода с пря «oiI"o выхода сумматора П; на выходе схемы со впадения 15 появится сигнал, соответствующий логической 55 единице, если код с прямого выхода сумматора 10 больше кода с инверсного выхода сумматора 11; па выходе схемы совпадения

1б будет сигнал, соответствующий логической единице, если код с прямого выхода вычитателя 12 не ме ньше кода с прямого выхода вььчитателя 18; наконец, на выходе схемы со впадения 17 будет сигнал, соответст вующий логической едииице, если код с прямого выхода вычитателя 12 не MI. HbjIIIB кода с и нверсного выхода вычитателя 18.

С вых одов схем совпадения сигналы в виде комби|нации л огических единиц и нулей поступают на входы сумматора 18, подсчитывающего число логических единиц па его входах в каждый момент времени.

На выходе сумматора 18 получают сигнал в виде огрубленного кода, поступающий для последующей обработки на сд вигающие регистры 5. С отводов многока нальных (по числу разрядов кода на его входе) сдвигающих регистров 5 сипналы в виде кодов IIIQступаю,т иа матрицу 5 ве.совых суммат оров.

Законы взвешивания для каждого весового сумматора различны, что, позволяет произв одить фильтрацию полезных сипналов по какому-либо параметру, например по частоте.

Предмет изобретения

1. Устройство для фильтрации сипналов, содержащее генератор опорного сипнала, к которому через фазорасщепитель подключены два фазовых детектора, два сдвигающих регистра, матрица весовых сумматоров и квадратичный c)IMIMBтор, отличающееся тем, что, с целью повышения отношения полезного сигнала к фазоманипулированной помехе, оно содержит два логических преобразователя, входы которых соединены с выходами фазовых детекторов, а выходы подключены ко входам соответствующих регист ров сдв:ига.

2. VlcTpoHcTBQ IIO п, 1, отличающееся тем, что в нем каждый логический преобразователь содержит четыре схемы совпадения, два сумматора, два вычитателя, выходной сумм атор и посл едователыно включенные иногоуровне вый кдантователь ам плитуды и сдвигающий регистр, выходы которого попарно соединены со входами двух сум маторов и двух вычитателей, подключенных через четыре схемы совпадения к входам выходного сумматора.

389631

Фиг. 1

Составитель Э. Митрошин

Корректоры: Л. Васильева н Н, Учакина

Техред T. Курилко

Редактор T. Орловская

Типография, пр. Сапунова, 2

Заказ 292G/14 Изд. № 770 Тираж 078 Подписное

ЦНИИПИ Государственного комитета Совета а1пнистров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5