Аналоговый регистр сдвига

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 11 1.1972 (№ 1739241/18-24) с,присоединением заявки ¹

Приоритет

Опубликовано 22.Ч111.1973. Бюллетень ¹ 34

Дата опубликования описания 14.XI I.1973

М. Кл. G 11c 27/ОО

Гасударственный комитет

Совета Министров СССР ло делам изобретений и открытий

УДК 681.337(088.8) Автор изобретения

А. Х. Мурсаев

Ленинградский ордена Ленина электротехнический институт им. В. И, Ульянова (Ленина) Заявитель

АНАЛОГОВЫЙ РЕГИСТР СДВИГА

Предлагаемое изобретение относится к аналоговой вычислительной технике, измерительной технике, может найти применение в радиотехнике, устройствах автоматического управления и других областях техники, где требуется точная по амплитуде и времени задержка аналоговых сигналов.

Известны схемы аналоговых регистров сдвига, содержащие запоминающие ячейки, например, конденсаторного типа, работающие по принципу последовательной перезаписи аналогового сигнала с одной запоминающей ячейки на другую.

Обычно передача сигнала осуществляется за два такта, в первом из которых информация со всех основных запоминающих ячеек записывается на промежуточные запоминающие ячейки, а во втором сигналы с промежуточных ячеек одновременно передаются на следующие основные ячейки. В таких схемах на каждый запоминаемый и сдвигаемый отсчет входного сигнала необходимо иметь две аналоговые запоминающие ячейки. При каждой перезаписи сигнала с ячейки на ячейку возникают ошибки передачи, которые накапливаются за время сдвига и при большой емкости регистра сдвига могут составить значительную величину.

Попытки повышения точности каждой запоминающей ячейки, например, за счет подбора запоминаемого напряжения по замкнутой схеме приводят к значительному увелнчешпо оборудования.

Целью предлагаемого изобретения является устранение указанных недостатков, т. е. повы5 шение точности передачи сдвигаемой информации и сокращение общего количества оборудования.

Цель достигается введением распределителя импульсов, коммутатора и дифференциального

10 усилителя постоянного тока.

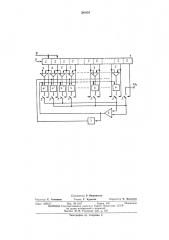

На чертеже изображена схема аналогового р егистр а сдв ига.

Предлагаемый регистр сдвига содержит цифровой регистр сдвига 1, триггерные ячейки 2

15 регистра сдвига, логические элементы «Iii:-Г»

8, аналоговые запоминающие ячейки 4, аналоговые ключи 5, дифференциальный усилитель 6 постоянного тока, инвертор 7, шину 8 сигнала сдвига аналоговой информации и шину 9 вы20 сокочастотных тактовых импульсов.

Сигнал IIO шине 8 сдвига подан на входы установки в единицу двух младших ячеек 2 цифрового регистра сдвига 1. На управляюгций вход регистра сдвига 1 поданы высокочастот25 ные тактовые импульсы по шине 9. Выходы ,всех соседник пар ячеек 2 регистра сдвига 1 под ключены и входам логических элементов

«НЕТ» 3, причем выход младшсго разряда подключен к запрещающему входу, а старше30 го — к разрешающему. Выходы элементоь

394854

«НЕТ» 3 подключены к управляющим входам аналоговых запоминающих ячеек 4. Выходы аналоговых запоминающих ячеек соединены с ключами 5, управляющие входы которых соединены с выходами соответствующих разрядов регистра сдвига 1. Выходы четных ключей

5 подключены на один из входов дифференциального усилителя 6, а нечетных ключей 5— на другой. Выход усилителя 6 соединен со входами всех нечетных запоминающих ячеек 4 и входом инвертора 7. Выход инвертора соединен со входами всех четных запоминающих ячеек 5. Входной сигнал U,> подключается ко входу усилителя с помощью ключа 5, управляющий вход которого соединен со старшим разрядом цифрового регистра сдвига.

Схема работает следующим образом.

Сигнал сдвига по шине 8 устанавливает триггеры младших разрядов в единичное состояние, при котором выходы этих разрядов возбуждены. Это состояние сохр а и я ется до прихода первого тактового импульса по шине

9. При этом через первый логический элемент

«НЕТ» на управляющий вход первой аналоговой запоминающей ячейки 4 подается сигнал, разрешающий запись, а на вход второй 4" и всех остальных ячеек 4 поданы сигналы, запрещающие запись.

Одновременно замыкаются ключи 5 и 5" (замыкается цепь обратной связи). На выходе усилителя 6 и на выходе первой запоминающей ячейки 4 подбирается напряжение, сводящее к нулю разбаланс напряжений на входе усилителя б. Через некоторое время, определяемо-. инерционностью усилителя 6 и запоминающей ячейки 4, сигналы на выходе соседних ячеек выравниваются, т. е. осуществляется перезапись информации со второй ячейки 4 на первую.

Следующий тактовый импульс сдгигает информацию в цифровом регистре сдвига 1, переводя его в состояние, при котором возбуждены выходы второго н третьего разрядов регистра сдвига 1. Теперь сигнал разрешения записи подан на вторую ячейку 4, а на всех остальных ячейках присутствуют сигналы, запрещающие запись. Замкнуты ключи 5" и 5", и по цепи обратной связи, вклю гающей усилитель 6 и инвертор 7, на ячейке 4" подбирается напряжение, равное напряжению на ячейке 4" .

После следующего тактового импульса возбуждаются третий и четвертый выхо,—:,:.. регистра сдвига, и аналогичным обри,",ом происходит перезапись напряжения с предыдущей запоминающей ячейки 4 на последующую и так далее.

Таким образом, через число тактов, рагпое количеству запоминающих ячеек, происходит сдвиг всей информации, хранившейся в ячейках 4 аналогового регистра, в соседние ячейки

60 с меньшими номерами и запись нового значепия входного сигнала в последнюю ячейку.

В процессе работы функции входных зажимов дифференциального усилителя 6 меняются. Каждыи из них поочередно оказывается либо входом следящей системы, лиоо входом цепи обратнои связи. Это приводит к тому, что ошибки, вносимые дифференциальным усилителем 6 из-за дреифа нуля и неравенства коэффициентов передачи по ра" íûì входам при каждой перезаписи, меняют знак и не накапливаются, а компенсируются. Таким образом, суммарные ошибки аналогового регистра сдвига существенно уменьшаются по сравнению с известными схемами.

Инвертор 7 служит для изменения знака коэффициента передачи замкнутой цепи подбора сигналов па запоминающих элементах таким образом, чтобы он был всегда отрицательным.

Общее количество аналоговых запоминающих ячеек равно количеству запоминаемых выборок и вдвое меньше, чем в известных схемах, Предмет изобретения

Аналоговый регистр сдвига, содержащий аналоговые запоминающие ячейки, отличаюи ийся тем, что, с целью повышения точности передачи сдвигаемой информации и сокращения количества оборудования, в устройство введены цифровой регистр сдвига с триггерными ячейками, элементы «НВТ», аналоговые ключи, дифференциальный усилитель постоянного тока и инвертор, причем выходы цифрового регистра сдвига через элементы «НЕТ» подключены к управляющим входам аналоговых запоминающих ячеек, запрещающие входы элементов «HE i » каждого разряда соединены с выходами предшествующего разряда цифрового регистра, выход каждой аналоговой запомипаюгцей ячейки подключен к аналогоьому ключу, соединенному с выходом соответствующего разряда цифрового регистра сдвиI.a, выходы всех четных аналоговых ключей подключены к одному из входов дифференциального усилителя постоянного тока, а нечетных — к другому входу.; выход дифференциального усилителя постоянного тока соединен со входами всех четных аналоговых запоминающих ячеек и входом инвертора, выход которого соединен со входами нечетных аналоговых запоминающих ячеек; шина сигнала сдвига соединена со входами установки в единицу младших разрядов пифрового регистра сдвигd, управляющие входы которого соединеныс шиной тактового сиг:ала, шина входного сигнала соединена со входом дифференциального уси,.ителя через аналоговый ключ, подключенный к старшему разряду цифрового регистра сдвига.

394854

Составитель P. Яворовская

Техред T. Курилко

Редактор Е. Семанова

Корректор Е. Блюмина

Типография, пр. Сапунова, 2

Заказ 3321/!7 Изд. № 1817 Тираж 576 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5