Патент ссср 399156

Иллюстрации

Показать всеРеферат

399156

ОПИСАНИЕ

ИЗОБЕЕТИНИЯ

К ПАТЕНТУ

Союз Советских

Социалистических

Республик

33BHcIlмый оТ патента №

М.Кл. С 06f, 3/14

G 06f, 1/00

Заявлено 14.Х.1969 (№ 1365099/18-24) Приоритет 8.XI 1968 № 15171/68, Швеция

IocIдарствеинь и комитет

Совета ь1ииистров СССР па делам изоеретеиий и открытий

Опубликовано 27.!Х.!973. Бюллстещ № 38

УДК 681.327.22(088.8) Дата опубликования описания 6.III.1974

Авторы изобретения

Иностранцы

Харальд Хуул (Норвегия) и

Бертил Норо и Рольф Эрикссон (Швеция) Иностранная фирма

«Телефонактиеболагет, Л. М. Эрикссон» (Швеция1

Заявитель

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДИОДНОЙ МАТРИЦЪ|

Предлагаемое устройство применимо в области автоматики и вычислительной техники и предназначено для индикации обратных токов в диодн ой м атр ице.

Известно устройство для контроля диодной матрицы, содержащее горизонтальные и вертикальные шины, подключенные через коммутаторы к источникам постоянного напряжения, в точках пересечения которых включены бистабильные элементы.

С целью обеспечения индикации неисправных диодов для контроля диодной матрицы введены два чувствительных элемента, входы которых через диоды подключены к горизонтальным шинам матрицы, и логические элементы, через которые выходы чувствительных элементов подключены к индикатору; чувствительные элементы выполнены на двух последовательно включенных транзисторах, а ко входу выходного логического элемента подключена шина положительного импульса управления.

Это обеспечивает индикацию обратных токов в точках пересечения диодной матрицы.

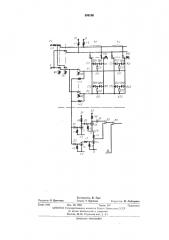

Предлагаемое устройство представлено на чертеже.

Оно содержит бистабильные элементы

Z11; Z12; Z21; Z22; реле с контактными парами

КК1, КК2, BR, СК, КК1, RR2, диоды ДС11, ДС21, ДВ! 1, ДС12, ДС22, ДВ12, ДВ22, Дl, Д2, ДЗ, резисторы гl, r2, гЗ, ггl, rr2, г4—

2 гl l, транзисторы Tl — Т4, логические элементы

Л l — ЛЗ.

Устройство для контроля диодной матрицы работает следующим образом.

Напряхкение и устройству для индикации подводится через клеммы El и Е2, причем напряжение Е1 должно быть больше напряжения Е2, например +24в и +5в соответственно, и клемму О, которая соответствует нулевому

1п потенциалу. После выбора точки пересечения в матрице должна быть проведена проверка диодов соответствующей вертикальной шины, а затем к стабильному элементу подается ток для проверки работоспособности диодов. При желании этот ток можно уменьшить. При выборе точки пересечения вертикальной шины и горизонтальной, т. е. точки А12, 812, С12, проверка начинается с включения реле ICR1 и подаче к точкам С11, С12... напряжения Е1, н соединении точек 811, 812 с нулевым потенциалом 0. Если все диоды в вертикальной шине исправны, то через них ток е пойдет, что и будет зафиксировано контрольным устройством

Затем при выборе точки пересечения А12, 812, С12 включается реле ряда KR2 и одно из реле BR или CR. При включении BR ток пойдет от Е1 через резистор r8, контакт реле BR, контакт реле KR. диод Д812, элемент Z12, контакт реле RR2, контакт реле BR зо и О. При включении реле С ток идет от Е1 че399156

10 5

Зо

3 рез сопротивление r8, контакт реле CR, контакт реле RR2, элемент Z12, диод ДС12, контакт реле AR1, контакт реле CR и О.

Если, однако, диод неисправен, например диод ДС11 имеет слишком высокий обратный ток, то произойдет следующее. При включении реле KR1 ток проходит от El через резистор rl, контакт реле КР1, диод ДС11, включенный в обратном направлеяии, элемент Zll, резистор RRl, диод Д1, резистор r4, подключенный параллельно к базе-эмиттеру транзистора

Тl, к Е2. Транзистор Тl открывается и шунтирует транзистор Т2.

Входное напряжение на логическом элементе пнверторе Лl возрастает, а напря>кение на выходе падает. 1хогда транзистор Т4 заперг, входные напряжения на входах логического элементы инвертора «НЕ И» Л2 будут соответственно высоким и низким, т. е. выходное напряжение возрастет. Входное напряжение на одном из входов логического элемента ипвертора «НЕ И» ЛЗ возрастает, напряжение на другом входе равно О, однако в определенный момент перед подачей тока через выбранную точку пересечения оно регулируется подачей поло>кительного импульса тока. Если все диоды в матрице исправны, то напряжение на выходе из инвертора ЛЗ имеет высокий потенциал. То же самое будет иметь место и при выходе одного из диодов из строя, если к нему не подается управляющий импульс. При подаче такого импульса к другому входу инвертора JM и при повреждении одного из диодов напряжение па выходе из инвертора ЛЗ упадет, что будет означать, что один из диодов матрицы повре>кден, в частности диод в выбранном столбце. Напряжение на выходе из инвертора ЛЗ может быть использовано для уменьшения тока, подаваемого к точке пересечения матрицы.

Если же, например, диод ДВ12 имеет слиш4 ком большой ток утечки, то произойдет следующее. При включении реле КИ ток идет от

Е2 через резистор r5, параллельный базе-эмиттеру транзистора ТЗ, диод Д2, резистор «2, элемент Z12, диод ДВ12, включенный в обратном направлении, контакт реле КИ, резистор r2 к

О. При этом транзистор ТЗ запирается, а транзистор Т4 открывается. Так как транзистор Тl заперт, то транзистор Т2 откроется, это означает, что напряжение на одном из входов инвертора Л2 возрастет, а на другом понизится, но в обратной полярности по сравнению с ранее описанным случаем. При этом так же, как и раньше, срабатывает инвертор ЛЗ, так что при подаче к нему положительного импульса, его выходное напряжение упадет, что означает выход из строя соответствующего диода.

Предмет изобретения

1. Устройство для контроля диодной матрицы, содержащее одинарные горизонтальные и двойные вертикальные шины, подключенные через коммутаторы к источникам постоянного напряжения, причем в точках пересечения включены через диоды бистабильные элементы, отличающееся тем, что, с целью обеспечения индикации неисправных диодов, устройство содержит индикатор, два чувствительных элемента, входы которых через диоды подключены к горизонтальным шипам, и логические элементы, через которые выходы чувствительных элементов подключены к индикатору, причем к выходному логическому элементу подключена шина положительного импульса управления.

2. Устройство по и. 1, отличающееся тем, по чувствительный элемент выполнен в виде усилителя на двух последовательно включенных транзисторах.

39S156

Составитель В. Заре

Техред Т. Курилко

Редактор Л. Цветкова

Корректор М, Лейзерман

Заказ 6445

Загорская типография

Изд. Ме 1953 Тираж 647 Подписное

ЦНИИГ1И Государственного комитета Совета Мшшстров СССР по делам изобретений и открытий

Москва, Ж,-35, Раушская наб., д. 4. 5