Частотно-импульсный функциональный преобразователь

Иллюстрации

Показать всеРеферат

< к 4% ь4

О П И И Е 399865

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 06Х.1971 (№ 1653814/18-24) с присоединением заявки №

Приоритет

Опубликовано ОЗ.Х.1973. Бюллетень № 39

Дата опубликования описания 20.III.1974

М. Кл. G 06f 15/20

Гасударственный комитет

Совета Министров СССР оо делам иеооретений и открытий

УДК 681 335 813 (088 8) Авторы изобретения

Г. О. Паламарюк, В. Н. Локтюхин и Н, И. Иопа

Рязанский радиотехнический институт

Заявитель

ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано в вычислительных и измерительных устройствах, обрабатывающих частотно-импульсную информацию.

Известен время-импульсный функциональный преобразователь, содержащий умножитель частоты, множительно-делительные блоки, реверсивные счетчики, логические триггеры и частотно-импульсный следящий блок.

Однако он имеет низкую точность функционального преобразования, обусловленную погрешностью ключевых элементов, нелинейностью характеристик и конечным значением коэффициента усиления усилителя.

Для повышения точности функционального преобразования устройства в нем входы вычитания реверсивных счетчиков множительноделительных блоков через умножитель частоты подключены к входу преобразователя, к одному входу триггера первого множительноделительного блока и через триггер к входу первой импульсно-потенциальной схемы «И»; другие импульсно-потенциальные схемы «И» через триггеры, вторые входы которых подключены к шине опорной частоты, присоединены ко вторым входам триггеров и к выходам реверсивных счетчиков множительно-делительных блоков, входы суммирования которых через соответствующие импульсно-потенциальные схемы «И» подключены к шине опорной частоты и к выходам триггеров множительно-делительных блоков.

Первые входы последних соединены с вы5 ходами предыдущих по номеру множительноделительных блоков.

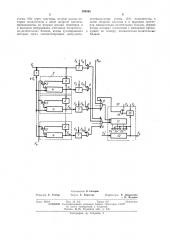

На чертеже приведена схема устройства.

Она содержит умножитель частоты 1, iifHQжительно-делительные блоки 2, состоящие из

10 триггеров 3, реверсивных счетчиков 4, импульсно-потенциальных схем «И» 5, импульсно-потенциальные схемы «И» 6, триггеры 7, две схемы «ИЛИ» 8 и 9, и частотно-импульсный следящий блок 10, состоящий из ревер1s сивного счетчика 11, управляемого делителя частоты 12, триггера 13 и группы схем

«И» 14.

Вход преобразователя подключен к входу

20 умножителя частоты 1, в котором входная частота F.„. умножается на коэффициент

К)1. Выход умножителя частоты 1 соединен с вычитающимн входами реверсивных счетчиков 4 множитель о-делительных блоков 2.

2s Кроме того, вход преобразователя подключен ко входу триггера 7 и ко входу триггера 3 первого множительно-делительного блока 2, выход которого соединен со входом триггера

3 второго множительно-делительного блока 2

30 и T.д.

399865 х!

F .

)х! г

+(i — 1) х. с х х! Fol xi (с — 1) 2 с, (5) откуда х ! х2—

Fo (2) ф! — 1) F! х х! с(! — 1) о (4) ф! — ) р! х

«! F(i — l) о

Выходы множительно-делительных блоков

2 соответственно связаны со входами триггеров 7, вторые входы которых подключены к шине опорной частоты F2, а выходы — к потенциальным входам импульсно-потенциальных схем «И» 6, соединенных соответственно своими импульсными входами с шинами образцовых частот F01, F02, ..., Fo . Выходы схем «И» 6 и шина образцовой частоты Foo через схемы «ИЛИ» 8 и 9 подключены к вычитающему и суммирующему входам реверсивного счетчика 11 частотно-импульсного следящего блока 10, в цепь обратной связи которой включены триггер 13 и импульснопотенциальная схема «И» 14. Выход импульсно-потенциального следящего блока 10 является выходом преобразователя.

Работа устройства заключается в следующем.

Входная частотно-импульсная последовательность Р„=Х поступает на вход умножителя частоты 1, умножающего входную частоту г„на коэффициент К)1=const. Использование умножителя 1 в функциональном преобразователе обеспечивает необходимое быстродействие.

Частотно-импульсная последовательность

kF„c выхода умножителя частоты 1 и входная F„- поступают на соответствующие входы последовательно соединенных множительноделительных блоков 2.

В множительно-делительном блоке 2, моделирующем квадратичную функцию, каждый импульс выходной частоты F,2, являющийся импульсом переполнения реверсивного счетчика 4, переводит триггер 3 в состояние, при котором в течение периода Т, входной частоты в реверсивный счетчик 4 записывается число F,Ò„, которое списывается импульсами частоты kF в течение периода Т„, выходной частоты F 2 первого однорегистрового множительно-делительного блока, т, е.

FoÒõ KF„° Të2 с (1) На выходе второго множительно-делительноr0 блока 2 аналогично г З х «3 о и на выходе (i — 1) -ro устройства, моделирующего степенную функцию х!

Частотно-импульсные последовательности (i=1, 2, 3 ..., m) поступают соответственно на входы триггеров 7 формирующих прямоугольные импульсы скважности которые управляют импульсно-потенциальными «И» 6 схемами.

Импульсы О,! заполняются импульсами образцовых частот F„, пропорциональных коэффициентам а! степенного ряда, аппроксимирующего воспроизводимую функцию. Тогда частота на выходе (i — 1) -ой схемы «И» 6 равна

Частоты F;, и образцовая частота Foo, соот20 ветствующая коэффициенту ряда, через схемы «ИЛИ» 8 и 9 в зависимости от знаков слагаемых степенного ряда поступают на суммирующий или вычитающий входы реверсивного счетчика 11 частотно-импульсного следящего блока 10, реализующей операцию

25 сложения частотно-импульсных последовательностей. Поскольку в цепь обратной связи следящего блока 10 включены триггер 13, на вход которого подается частота F3 и импульс30 но-потенциальная схема «И» 14, на вход которой подается частота F<, то помимо суммирования частотно-импульсный следящий блок

10 реализует и множительно-делительную опер ацию.

В установившемся режиме выражение для выходной частоты следящего блока 10 имеет вид ссс (! 1) (6) г, . г,. г(1- )

i=0

Из моделирующей зависимости (6) устройства видно, что оно производит также множительно-делительную операцию независимых

45 переменных, представленных в виде частоты.

Предмет изобретения

Частотно-импульсный функциональный пре50 образователь, содержащий умножитель частоты, множительно-делительные блоки с триггерами, импульсно-потенциальными схемами

«И» и реверсивными счетчиками, триггеры и частотно-импульсный следящий блок, входы

55 которого через схемы «ИЛИ» и импульсно-потенциальные схемы «И» подключены к шинам образцовых частот, отлича!ощийся тем, что, с целью повышения точности, в нем входы вычитания реверсивных счетчиков множи60 тельно-делительных блоков через умножитель частоты подключены ко входу преобразователя, к одному входу триггера первого множительно-делительного блока и через триггер ко входу первой импульсно-потенциальной

65 схемы «И»; другие импульсно-потенциальные

399865

Составитель О. Сахаров

Техред E. Борисова

Корректоры: E. Давыдкина и В. Петрова

Редактор Е. Гончар

Заказ 569j4 Изд. ¹ 215 Тираж 647 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, уК-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 схемы «И» через триггеры, вторые входы которых подключены к шине опорной частоты, присоединены ко вторым входам триггеров и к выходам реверсивиых счетчиков миожительцо-делительцых блоков, входы суммирования которых через соответствующие импульснопотенциальные схемы «И» подключены. к шине опорной частоты и к выходам триггеров множптельно-делительных блоков, первые входы которых соединены с выходами преды5 дущих по номеру мцожительно-делительиых блоков.