Патент ссср 402172

Иллюстрации

Показать всеРеферат

402I72

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик

Зависимое от авт. свидетельства №

Заявлено 05.1V.1971 (№ 1643882/26-25) с присоединением заявки ¹

Приоритет

Опубликовано 12.Х.1973. Бюллетень ¹ 41

Дата опубликования описания 20.II.1974

М. Кл. Н 05k 1/00

Н 011 7/00

Государственное комитет

Совета Министров СССР оо делам изооретвнии и открытий

УДК 621.382:621.317.799 (088.8) Авторы изобретения

Ю. В. Беленький, Г. И. Берлинков и В. С. Гальперин

Заявитель

1"- П 1Б

4 й;;:;14

СПОСОБ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ СХЕМ ОТ ВЛИЯНИЯ

ПАРАЗИТНЫХ ТРАНЗИСТОРОВ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в интегральных схемах на МДП-транзисторах.

В интегральных схемах на МДП-транзисторах могут появляться паразитные транзисторы между диффузионными областями при пересечении последних «высоковольтными» шинами управляющих сигналов. Особенно недопустимо формирование паразитных транзисторов в узлах хранения информации, поскольку в результате резко уменьшается время хранения за счет разряда узловых емкостей схемы токами паразитных транзисторов, значительно превышающими токи утечки узлов интегральной схемы. При создании интегральных схем принимают различные меры для устранения вредного влияния паразитных транзисторов.

Известен способ защиты интегральных схем от влияния паразитных транзисторов, основанный на увеличении толщины окисла под коммутационными алюминиевыми шинами при сохранении тонкого окисла под затворами активных транзисторов. При этом увеличивается пороговое напряжение паразитных транзисторов, образовавшихся под толстым слоем окисла.

Для достижения лучших результатов используют подложку из материала с другим удельным сопротивлением, но при этом существенно ухудшаются характеристики активных транзисторов в схеме.

Согласно способу Бридуэлла, вводят разделительную диффузию п+-типа в область между защищаемыми диффузионными шинами.

Однако в результате усложняется топология схемы, требуется дополнительная диффузия, например диффузия фосфора, при изготовле10 нии интегральных схем на МДП-транзисторах с индуцированным р-каналом, и увеличивается площадь, занимаемая схемой.

Цель изобретения — создание способа защиты интегральных схем от влияния паразит15 ных транзисторов без усложнения топологии и технологии изготовления схемы и без увеличения занимаемой ею площади.

Согласно изобретению, поставленная цель достигается подачей напряжения смещения

20 определенной полярности на контакт подложки интегральной схемы относительно контакта земли. Полярность постоянного напряжения, подаваемого на подложку, зависит от типа канала транзисторов в схеме: положительное

25 напряжение — для схем с р-канальными транзисторами, отрицательное — для схем с и-канальными транзисторами.

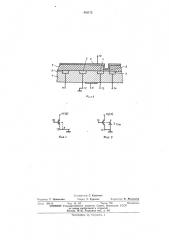

На фиг. 1 представлена часть кремниевого кристалла с диффузионными областями, пере30 секаемыми алюминиевой коммутационной ши402172 ной; на фиг. 2 — паразитный транзистор, который может возникнуть между двумя диффузионными областями, если напряжение на пересекающей их алюминиевой шине превышает величину порогового напряжения для данной толщины диэлектрика (подложка-кристалл соединена с контактом земли); на фиг. 3 — паразитный транзистор, на подложку которого подано положительное смещение относительно истока.

Интегральная схема на МДП-транзисторах выполнена на полупроводниковом кристаллеподложке 1. Диффузионные области 2 — 5 (причем область 3 соединена с шиной земли) пересекаются металлической коммутационной шиной 6. Поверхность кристалла отделена от коммутационной шины толстым слоем диэлектрика 7, например SiOq, Под затвором активного транзистора имеется тонкий слой 8 диэлектрика. Кроме того, выполнены контакт

9 подложки, вывод 10 коммутационной шины; выводы 11 — 14 диффузионных областей.

Известно, что эффективное значение порогового напряжения МДП-транзисторов зависит от величины напряжения между истоком и подложкой из-за влияния подложки на ток стока транзистора. Для тонкого слоя окисла

ЛU„, = — k,(2ур+ U, „— )г 2 р),— где k> — тангенс угла наклона функции;

cp> — уровень Ферми;

U„, — напряжение между затвором и подложкой.

Таким образом, при подаче напряжения смещения на подложку пороговые напряжения всех транзисторов, изготовленных на данном полупроводниковом кристалле (кремния), увеличатся. Однако отношение увеличения порогового напряжения транзисторов, из которых состоит реализуемая схема, к соответствующему увеличению напряжения транзисторов с

5 толстым слоем диэлектрика под затвором (пар азитных транзисторов) равно отношению толщин слоев диэлектриков. Для изготавливаемых в настоящее время интегральных схем на МДП-транзисторах это отношение прибли10 жается к 10. Поэтому, подавая небольшое напряжение смещения 1 — 2 в, можно получить значительное увеличение порогового напряжения паразитных транзисторов при незначительном увеличении этого параметра для

15 остальных транзисторов.

Например, подавая на подложку напряжение 2 в, получим ЛУпор То«. 0,95 в при толшине тонкого окисла d«, o«.=1800 А, ЛУ„р„,„„= 7,0 в при толщине толстого

20 о окисла d„„.„„.„13000 А, концентрация носителей N = 10"см- (К=0,85 в).

25 Предмет изобретения

1. Способ защиты интегральных схем от влияния паразитных транзисторов, отличающийся тем, что, с целью упрощения способа, 30 на подложку схем относительно шины земли подают постоянное напряжение.

2. Способ по п. 1, отличающийся тем, что для схем с р-канальными транзисторами подают положительное напряжение.

35 3. Способ по п. 1, отличающийся тем, что для схем с и-канальными транзисторами подают отрицательное напряжение.

402172

Фиг. 2

Составитель С. Каленков

Техред Т. Курилко

Корректор В. Жолудева

Редактор T. Орловская

Заказ 306/! 6 Изд. ¹ 135 Тираж 755 Подписное

Е1НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4)5

Типография, пр. Сапунова, 2