Патент ссср 403069

Иллюстрации

Показать всеРеферат

403069

О П

Союз Советскик

Социалистинеских

Республик

Зависимое от авт. свидетельства №

Л1. Кл. H 03k 21!06

Заявлено 03«Х11.1971 (¹ 1720449/26-9) с присоединением заявки М

Приоритет

Опубликовано 19.Х,1973, голгг,TcllI> X 42

Дата опубликования описания 15.111.1974

Государствеиный комитет

Соввта Мииистрав СССР аа делам изабретений и открытий

Ъ ДК 621.374А (088.8) Авторы изобретения

P. В. Багдасарова и Г. Л. Рубинштейн

Заявитель

ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ

КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике.

Известен делитель частоты с переменным коэффициентом деления, содержащий и-разрядный счетчик на элементах «И» («ИЛИ»)—

«НЕ», запоминающее устройство и схему управления. Такой делитель имеет ограниченное быстродействие, обусловленное введением импульса сброса счетчика между входными импульсами. Это по крайней мере в два раза снижает быстродействие делителя.

Кроме того, известный делитель имеет ограниченные функциональные возможности, обусловленныс тем, что длительность задержки линии т;,, должна быть больше длительности входных импульсов в„и больше длиивх тельности переходных процессов в счетчике т„,р. При больших т„т,, возрастает и в этом случае требуется введение дополнительной схемы формирования, укор ачивающей входной импульс.

Предлагаемый делитель отличается от известного тем, что в целях расширения функциональных возможностей и повышения быстродействия в нем дополнительно установлена схема совпадения на n + 1 вход, п-разрядный счетчик на элементах «И» («ИЛИ»)-«НЕ» выполнен на триггерах 1 — К-типа, а схема управления — -на дешифраторе и и схемах совпадения. Причем выходы элементов

«И» («ИЛИ») — «НЕ», соединенных с вентилями К триггеров и разрядов счетчика, подключены и входам схемы совпадения на n+1 вход и дешифратора, выход которого подключен к одним входам и схем совпадения схемы управления. Другие входы схем совпадения схемы управления соединены с выходами за10 помпнающего устройства, а их выходы подклгочены к соответствугощим дополнительным входам вентилей К триггеров и разрядов счетчика.

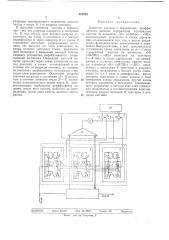

На чертеже изображен предлагаемый дели15 тель. Он содержит быстродействугощий счетчик 1 с параллельной подачей счетных импульсов на триггерах 2 I — К-типа, каждый

113 которых построен на шести мпоговходовых логических элементах 3, «И» («ИЛИ»)—

20 «НЕ». Выходы 4 элементов, управляющих вентилем К-триггера всех разрядов счетчика, подключены к схеме 5 уточнения и к дешифратору 6 схемы 7 управления, который через ппвертор 8 и п схем 9 совпадения, управляе2s мых запоминающим устройством 10, соединен с входами 1! К-триггеров всех разрядов счетчика. Входной сигнал поступает на вход счетчика и схему уточнения; выходом делителя является выход схемы уточнения. Причем

30 выход схемы совпадения, управляемой г-м

403069

Делитель частоты с переменным,коэффициентом деления, содерж" ùèé и-разрядный счетчик а элементах «И» («ИЛИ») — «НЕ», запоминающее устройство и схему управления, отгичагощиасл тем, что, с целью расширения функциональных возможностей и повышения быстродействия, в нем дополнительно

10 установлена схема совпадения па n+- 1 вход, и-разрядный счетчик»а элементах «И» («ИЛИ») — «HL» выполнен а триггерах

I — К-типа, à схема управления — на дешифраторе и и схемах совпадения, причем выхо15 ды элементов «И» («ИЛИ») — «НЕ», соединенных с вентилями К триггеров п разрядов счетчика, подключены к входам схемы совпадения па и + 1 вход и дешифратора, выход которого подключен к одним входам и схем

20 совпадения схемы управления, другие входы которых соединены с выходами запоминающего устройства, а выходы этих схем совпадения подключены к соответствующим дополнительным входам вентилей К триггеров и раз25 рядов счетчика.

1

ЦНИИПИ Заказ 510!16 Изд. ¹ 2042

Тираж 780 Подписное

Типог; 4 пи, пр. Сапунова, 2 разрядом запоминающего устройства, подключается к входу 11 г-го разряда счетчика.

В исходном состоянии счетчик 1 переполнен — все его разряды находятся в состоянии

«1». В этом случае, если входной импульс отсутствует, на схему 5 уточнения и с выхода дешифратора 6 через инвертор 8 па схемы 9 совпадения поступает разрешающий потенциал. На выходах тех схем совпадения, па входы которых поступает также разрешающий потенциал с инверсных выходов запоминающего устройства, вырабатывается запрещающий потенциал. Очередной входной импульс проходит через схему уточнения на выход делителя, а также устанавливает в состояние «0» те разряды счетчика, на которые не поступает запрещающего потенциала с выходов схем совпадения. Остальные разряды счетчика остаются в состоянии «1». В результате в счетчик записано число 2" — Л7, являющееся дополнительным кодом числа N, соответствующего требуемому коэффициенту деления, после чего счетчик работает до переполнения. Затем цикл работы делителя повторяется.

Предмет изобретения