Устройство для вычисления функции видаz =. kv'x^ + у

Иллюстрации

Показать всеРеферат

есксо озтеМ

gATfti . t. C-ТсХНМв1ЕСКА%

404082

И Е

Союз Советских

Социалистических, Республик

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 16Х1.1.971 (№ 1672643/18-24) с присоединением заявки №вЂ”

Приоритет—

Опубликовано 26.Х.1973. Бюллетень № 43

Дата опубликования описания 21.III.1974

М. Кл. G 06f 7/38

Государственный комитет

Соввта Министров СССР но делам изобретений и открытий

УДК 681.325.5(088.8) Авторы изобретения

Ю. В. Тимошин, Н. М. Гельман, А. А. Резник и В. Д, Шкляревский

Заявитель

Киевская экспедиция Украинского научно-исследовательского геологоразведочного института

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ ВИДА

Z = Ю Л 2 + УЯ

Z=ÊÐÕ + У, Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств дискретной автоматики и цифровых вычислительных машин.

Известны устройства для вычисления функции вида содержащие два регистра, связанные входами с шинами переменных, а выходами через две группы схем «И», другие входы которых связаны с выходами двух схем задержки, со входами третьего регистра, причем вход первой схемы задержки связан с первой шиной приращений, а вход второй схемы задержки через третью схему «И», другой вход которой подключен к выходу третьего регистра, — co второй шиной приращений, схему сравнения, логические схемы., Недостатками в известных устройствах является отсутствие контроля результатов вычислений и, следовательно, недостаточная надежность работы, а также наличие многоразрядного сумматора, в котором хранится величина (Х +У ), или наличие выходного регистра.

Предлагаемое устройство, с целью упрощения и повышения надежности его работы, содержит четвертый регистр, выходы первого и второго регистров связаны со входами схемы сравнения, выход которой связан со входами четвертой группы схем «И», другими входами связанных с выходами второго регистра, а вы5 ходами — с выходными шинами устройства; другие выходы обеих схем задержки связаны со входами третьего регистра; входы четвертого регистра связаны с двумя шинами переменных, первой шиной приращений и выхо10 дом третьей схемы «И».

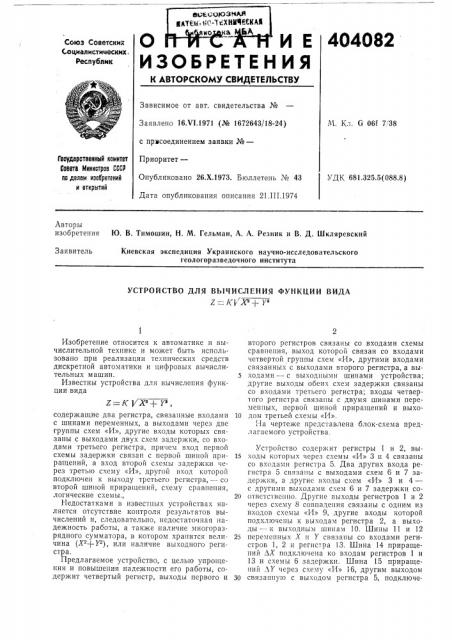

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит регистры 1 и 2, вы15 ходы которых через схемы «И» 3 н 4 связаны со входами регистра 5. Два других входа регнстра 5 связаны с выходами схем 6 и 7 задержки, а другис входы схем «И» 3 и 4— с другими выходами схем 6 и 7 задержки со20 ответственно. Другие выходы регистров 1 и 2 через схему 8 совпадения связаны с одним из входов схемы «И» 9, другие входы которой подключены к выходам регистра 2, а выходы — к выходным шинам 10. Шины 11 и 12

25 переменных Х и У связаны со входами регистров 1, 2 н регистра 13. Шина 14 приращений ЛХ подключена ко входам регистров 1 и

13 и схемы 6 задержки. Шина 15 приращений ЛУ через схему «И» 16, другим выходом

30 связа|шую с выходом регистра 5, подключе404082 на ко входам регистров 2, 13 и схемы 7 задержки.

Вычисление функции

Z К!./Л2+ Уй осуществляется устройством в соответствии со следующим алгоритмом. Так как

Z = VX + Y = V(X ) + (Г)*, где

Х = Х+ ЛХ;

Г= Y — ЛУ, (2) (3) то очевидно (2Х+ ЛХ) ЛХ = (2 Y — Л Y) Л У, причем, если Х = Г, то

Z = P 2Х = P 2 Y и У вЂ” Х = ЛХ+ Л У, (4) Таким образом, при заданных значениях Х и У величины Z могут быть определены следующим образом:

1. сравнить величины Х и У; если Х= У, то

Z= 2Х; если Х У, то

Z=Ê1 Х -+ V, 2. определить Х, из выражения (2) Х,—=

= Х+ЛХ (2) при ЛХ = 1;

3. из выражения (4) определить ЛУ;

4. из выражения (3) определить Г,;

5. сравнить Х, и Г<., ссли Х < — — Гь то, = 2Х 1, если Х 1 У,, то, пользуясь вышеуказанным алгоритмом, найти Х и У >, и т.д.

Устройство работает следующим образом.

По шинам 11 и 12 величины Х и У заносятся в регистры 1 и 2. Затем по шине 14 в регистр 1 на суммирующие входы подаются сигналы приращений ЛХ, и в регистре 1 накапливается величина (ЛХ+Х). В регистр 2 с шины 15 приращений ЛУ через схему «И» на вычитающий вход поступают сигналы ЛУ, и в нем формируется код числа У вЂ” ЛУ. В регистр 5 поступают сигналы приращений ЛХ через схему 7 задержки, код числа Х из регистра 1 через схему «И» 3 со сдвигом а один разряд влево, сигналы приращений ЛУ через схему «И» 16 и схему 7 задержки и с регистра 2 через схемы «И» 4 обратный код числа У со сдвигом на один разряд влево.

В регистре 5 таким образом образуется код числа. (2Х+ ЛХ) ЛХ вЂ” (2Y — ЛУ) ЛУ

При этом через схему «И» 16 проходит на один сигнал ЛХ такое количество сигналов

ЛУ, при котором в регистре 5 код этой величины становится равным пул1о. Сигнал с выхода регистра 5 закрывает схему «И» 16, а в

)О регистр 1 снова поступает сигнал ЛЛ, и т. д., до тех пор, пока числа, записанные в регистрах 1 и 2, не стМ1ут равными. В момент их равенства коды па обоих регистрах становятся равными искомой величине 7 и выдаются

15 через схемы «И» 9 а выходные шины 10, Для контроля результата вычислений устройство содержит регистр 13, па который поступают прямой код числа Х и обратный код числа У. В регистре 13 хранится код числа

1(роме того, в регистр 13 а входы вычитания поступают сигналы ЛХ и ЛУ. В момент срабатывания схемы сравнения 8 регистр 13 должен находиться в нулевом состоянии.

Предмет изобретения

Устройство для вычисления функции вида

Z= :К )/. (+ )", 30 содержащее два регистра, связанные входами с шинами переменных, а выходами через две группы схем «И», другие входы которых связаны с выходами двух схем задержки, со входами третьего регистра, причем вход первой

35 схемы задержки связан с первой шиной приращения, а вход второй схемы задержки через третью схему «И», другой вход которой подключен к выходу третьего регистра,— со второй шиной приращений, схему сравнения, 40 логические схемы, отличающееся тем, что, с целью упрощения устройства и повышения надежности его рабо1ы, оно содержит четвертый регистр, выходы первого и второго регистров связаны со входами схемы сравнения, 45 выход которой связан со входами четвертой группы схем «И», другими входами связанных с выходами второго регистра, а выходами — с выходными шинами устройства; другие выходы схем задержки связаны со входа50 ми третьего регистра; входы четвертого регистра связаны с двумя шинами переменных, первой шиной приращений и с выходами третьей схемы «И».

404082

11 Х

Составитель В. Белкин

Техрсд Е. Борисова

Корректор В. Жолудева

Редактор А. Батыгин

Типография, пр. Сапунова, 2

Заказ б!О/7 Изд. № !83 Тираж 647 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобоетений и открытий

Москва, 5К-35, Раушская наб., д. 4/5