Патент ссср 405178

Иллюстрации

Показать всеРеферат

! я%тент :с-: = 1. : "- библиоте,1., МЕй, ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

405I78

Союз Советскии

Социалистицеских

Республик

Зависимое от авт. свидетельства №

М. Кл. H 03k 19/08

Заявлено 10.ll.1972 (№ 1746668/26-9) с присоединением заявки №

Приоритет

Опубликовано 22.Х.1973. Бюллетень № 44

Дата опубликования описания 17Х.1974

Государственный комитет

Совета Министров СССР

Ао делим изейретений и открытий УДК 681.325.65(088.8) Авторы изобретения

Ю. Е. Наумов и И. Ф. Пучков

Заявитель

Московский ордена Ленина авиационный институт им. Серго Орджоникидзе

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИЛИ» НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к цифровой технике и микроэлектронике.

Известны логические элементы «ИЛИ» на

МДП транзисторах, содержащие два инвертора, каждый из которых состоит из инвертирующего транзистора одного типа проводимости с последовательно включенным нагрузочным транзистором противоположного типа проводимости, затворы которых объединены, m входных транзисторов противоположного типа проводимости, шину питания.

Предлагаемый элемент отличается от известных тем, что в нем входные транзисторы подключены затворами к выходу первого и входу второго инверторов, истоками †входным шинам элемента, а стоками — к выходу первого инвертора и через резистор к общей шине, причем исток нагрузочного транзистора первого инвертора подключен к дополнительной шине питания.

Это позволяет повысить помехоустойчивость схемы путем создания неоднозначной передаточной характеристики с гистерезисом.

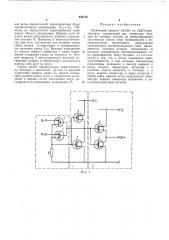

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 — передаточная характеристика.

Устройство состоит из инверторов 1 и 2, каждый из которого содержит инвертирующий

3 и 4 и нагрузочный 5 и 6 транзисторы (например, инвертирующие транзисторы с каналами п-типа, а нагрузочные с каналами р-типа), т входных транзисторов 7, например, с индуцированными каналами р-типа, резистора 8.

Устройство работает следующим образом.

5 При нулевом уровне напряжения на входных шинах входные транзисторы 7 закрыты, на затвор инвертирующего транзистора 3 поступает напряжение низкого уровня. На выходе первого инвертора напряжение высокого

1о уровня, равное Еь Напряжение Е1 выбирается таким, что оно превышает порог отпирания транзистора 4, поэтому на выходе всей схемы напряжение низкого уровчя (U», = О).

Повышение напряжения на одной из вход15 ных шин до величины, равной Е1+ Уу (У7— пороговое напряжение входных транзисторов), приводит к отпиранию соответствующего входного транзистора и инвертирующего транзистора 3 первого инвертора 1 и запиранию

20 транзистора 4. На выходе схемы при

У,„)Е1+ U> устанавливается напряжение высокого уровня (фиг. 2), равное Е .

Понижение напряжения на входной шине

2S приводит к выключению входного транзистора при напряжении, равном Uy, так как на затворе входных транзисторов после включения транзистора 3 установилось напряжение, близкое к нулевому уровню. П ар а метры тр а н30 зисторов 7 и 3 должны удовлетворять условию U7 (Уз ; в противоположном случае ле405178

Риг E вая ветвь передаточной характеристики будет соответствовать напряжению U, Uq. Поэтому на передаточной характеристике появляется область гистерезиса. Ширину этой области можно регулировать, изменяя напряжение питания Еь Выигрыш в помехоустойчивости при этом достигается для входных помех обоих знаков (отпирающих и запирающих), его величина равна Е I,. Высокое напряжение на выходе первого инвертора 1 ниже напряжения отпирания схемы на величину U>. Второй инвертор 2 восстанавливает высокий логический уровень и обеспечивает возможность работы схем друг на друга.

Схемы имеют передаточную характеристику, близкую к идеальной, так как ее высокий логический уровень равен Е>, низкий логический уровень равен нулю, а напряжение включения и ширина петли гистерезиса могут регулироваться изменением напряжения Е,.

Ь

Ег ! ! !

1

Предмет изобретения

Логический элемент «ИЛИ» на МДП-транзисторах, содержащий два инвертора, каждый из которых состоит из инвертирующего транзистора одного типа проводимости с последовательно включенным нагрузочным транзистором противоположного типа проводимости, затворы которых объединены, т

10 входных транзисторов противоположного типа проводимости, шину питания, о т л и ч а юшийся тем, что, с целью повышения помехоустойчивости, в нем входные транзисторы подключены затворами к выходу первого и

15 входу второго инверторов, истоками — к входным шинам элемента, а стоками — к входу первого инвертора и через резистор к общей шине, причем исток нагрузочного транзистора первого инвертора подключен к до20 полнительной шине питания.!

l !

6 ! (1 ! !

Юыг ! ! ! (!

406178

Е (/7 Рл (/7

Ри8 3

Составитель А. Федорова

Техред E Борисова

Корректор Л. Орлова

Редактор E. Караулова

Типография, пр. Сапунова, 2

Заказ 851/12 Изд. № 2073 Тираж 780 Подписное

ЦНИИПИ Государствевного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб,, д. 4/5