Цифровой регистратор однократных импульсных

Иллюстрации

Показать всеРеферат

., й:".. г, 407237

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

М. Кл. G 01г 13/02

G 016 5 245

Заявлено 25.У1.1971 (№ 1669461/26-9) с присоединением заявки №

Приоритет

Опубликовано 21.XI.1973. Бюллетень № 46

Дата опубликования описания 10.IV.1974

Гасударственный комитет

Совета Министров СССР па делам изобретений и открытий

УДК 621.317.35(088.8) Авторы изобретения

С. С. Караваев, В. В. Панин, А. В. Хомутов и К. К. Щегольков

Заявитель

Московский Ордена Трудового Красного Знамени инженернофизический институт

ЦИФРОВОЙ РЕГИСТРАТОР ОДНОКРАТНЫХ ИМПУЛЬСНЪ|Х

СИ ГНАЛОВ

Йзобретение может быть использовано в измерительной технике для регистрации однократных импульсных сигналов с быстроменяющейся начальной и медленноменяющейся оконечной фазой (частью) сигнала, при наличии

Шумов на входе регистратора и в случае, когда момент начала сигнала заранее неизвестен.

Известны цифровые регистраторы однократных импульсных сигналов, содержащие последовательно включенные датчик, скоростной 10 блок амплитудного анализа, параллельные выходы которого через вентили и шифраторы подключены ко входам сдвиговых регистров, соединенных как и вентили с тактовым генератором. 15

Однако в известных регистраторах при хранении информации, накопленной при регистрации даже не очень продолжительных сигналов, необходим значительный объем памяти.

С целью сокращения объема запоминаемой 20 информации при регистрации сигналов с бы-1 стропротекающей начальной и медденноменяющейся о конечной фазой в предлагаемый регистратор введены блок отбора событий, блок управления, блок анализа медленноменяющей- 25 ся амплитуды сигнала с сумматором, второй шифратор и ферритовый запоминающий узел, причем к выходу датчика подключены блок анализа медленноменяющейся амплитуды, который соединен через второй шифратор с за- З0

2 поминающим узлом, и блок отбора событий, выходы которого подключены к делителю частоты и двум вентилям, один из которых включен между тактовым генератором и формирователем тактовых серий, другой — между сумматором блока анализа медленноменяющейся амплитуды и блоком управления, который соединен с блоком отбора событии, вторым шифратором, делителем частоты, сдвиговыми регистрами и ферритовым запоминающим узлом, который дополнительно соединен с выходами сдвиговых регистров и счетчиком.

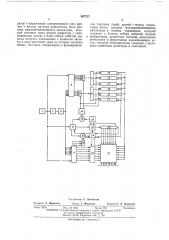

На чертеже дано предлагаемое устройство.

Выход датчтека 1 соединен с входами схемы 2 выделения модуля, скоростного блока 3 амплитудного анализа, блока 4 анализа медленноменяющейся амплитуды сигнала и блока 5 отбора событий. Выход схемы 2 через схему разветвления 6 соединяется со входами блоков 3 и 4. Выходы блока 3 через блоки 7 и

8 групп вентилей присоединены ко входам шифраторов 9 и 10, выходы которых, в свою очередь, подключены ко входам сдвиговых регистров 11, 12 и 13. Управляющие выходы вентилей блоков 7 и 8 соединены с выходами тактового генератора 14, который через вентиль

15 подключен к задающему генератору 16.

Управляющий выход вентиля 15 соединен с одним из выходов блока 5.

Выходы тактового генератора 14 подключены к сдвиговым входам регистров 11 — 13 и

17 — 19. Выходы блока 4 соединены со входами шифратора 20, информационные выходы последнего подключены к кодовым шинам ферритового запоминающего узла 21, к которым, в свою очередь, также присоединены информационные выходы регистров 11 — 13 и 17 — 19.

Выходы блока 4 через сборку 22 и вентиль 23 соединены со входом блока управления 24, выходы с которого заводятся на входы блока 5, регистров 11 — 13, шифратора 20, ферритового запоминающего узла 21 и на счетчик 25.

Помимо этого один из входов блока управления 24 соединен с одним из выходов счетчика 25, Счетный вход счетчика 25 через схему 26 деления частоты соединен с задающим генератором 16. Управляющие входы схемы 26 подключены к выходам счетчика 25 и блоку управления 24.

В процессе регистрации сигнала резличаются три режима работы: режим «ожидание», режим «регистрация» и режим «перезапись» накоплений информации во внешние устройства.

В режиме «ожидание» работает первый (быстрый) узел регистрации, состоящий из блоков 3, 7 — 15 и 17 — 19. Сигнал с датчика 1 попадает на «знаковый» вход блока 3, в котором анализируется знак сигнала. Одновременно сигнал, проходя через схему 2 и разветвитель 6, попадает на другие («сигнальные») входы блока 3. Высокий потенциал на какомлибо входе блока 3 опкрывает соответствующие вентили в блоках 7 и 8, в результате чего сигнал на соответствующем входе блока 3 превышает порог срабатывания данного порогового устройства.

Таким образом, в блоке 3 производится амплитудная дискриминация модуля входного сигнала.

Импульсы от задающего генератора 16, проходя через вентиль 15, который в этом режиме открыт «высоким» потенциалом, поступающим от блока 5 отбора событий, создают на выходе тактового генератора 14 две сдвинутые на полпериода друг относительно друга синхронизирующие серии импульсов. Первой серией импульсов опрашиваются вентли блока 8, второй — блока 7.

Импульсы с выходов блоков 7 и 8 устанавливают коды на шифраторах 9 и 10, соответствующие номеру порогового устройства с наибольшим порогом, срабатывающего к данному моменту времени. Синхронно с импульсами первой тактовой серии код с блока 9 передается на одвиговые регистры 11, 12 и 13; сдвиг кода на этих регистрах осуществляется импульсами этой же серии. Код, установленный на шифраторе 10, подается на регистры 17, 18 и 19, а затем сдвигается в них синхронно с импульсами второй тактовой серии.

Работа регистратора в этом режиме длится до тех пор, пока блок 5 отбора событий не от5

Зо

45 ключит вентиль 15. С этого момента прекращается опрос блоков 7 и 8 и сдвиг в регистрах 11, 12 и 13. Количество разрядов регистров и частота тактовых серий выбираются таким образом, что информация о регистрируемом сигнале за время срабатывания блока 5 отбора событий не теряется.

В режиме «ожидание» выходные импульсы блошка 4 также подаются на шифратор 20, однако информация, заносимая в этот шифратор не сохраняется, так как в этом режиме цепи опроса шифратора 20 блокированы вентилем

23. В момент переключения блока 5 изменяется режим работы регистратора. «Высоким» потенциалом с выхода блока 5 открывается вентиль 23 и включается схема 26. С это)го момента импульсы от задающего генератора 16, проходя через схему 26 деления частоты, попадают на вход счетчика 25, который начинает фиксировать время протекания сигнала.

В этом режиме работы регистратора модуль исследуемого сигнала дискриминируется пороговыми устройствами блока 4, выходные импульсы которых свидетельствуют о факте пересечения сигналом соответствующего порогового уровня и устанавливают на шифраторе 20 код, соответствующий номеру последнего, срабатывающего к данному моменту времени, порогового устройства.

Одновременно импульсы от блока 4, проходя через сборку 22 и вентиль 23, поступают в блок управления 24, который синхронно с этими импульсами передает показания шифратора 20 и счетчика 25 в ферритовый запоминающий узел 21. Синхронно с импульсом переполнения счетчика 25, поступающим в блок управления 24, работа в режиме «регистрация» прекращается.

Вслед за этим блок управления 24 выраба. тывает команду «перезапись», по которой включаются внешние накопители; с помощью синхроимпульсов от этих накопителей блок управления 24 управляет перезаписью информации из запоминающего устройства 21 во внешние накопители. По окончании перезаписи блок управления 24 переводит регистратор заново в режим «ожидание».

Предмет изобретения

Цифровой регистратор однократных импульсных сигналов, содержащий последовательно включенные датчик, скоростной блок амплитудного анализа, параллельные выходы которого через вентили и шифраторы подключены ко входам сдвиговых регистров, соединенных, как и вентили, с формирователем тактовых серий, тактовый генератор, соединенный со счетчиком через делитель частоты, отлича сщий ся тем, что, с целью сокращения объема запоминаемой информации при регистрации сигналов с быстропротекающей начальной и медленноменяющейся оконечной фазой, введены блок отбора событий, блок управления, блок анализа медленноменяющейся амплитуды сигнала с сумматором, второй шиф4О7237

Составитель С. Лукинская

Техред Т. Миронова

Корректор Л. Царькова

Редактор Т. Морозова

Заказ 783/9 Изд. № 1044 Тираж 755 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 5К-35, Раушская наб., д. 4/5

Типография пр. Сапунова, 2 ратор и ферритовый запоминающий узел, причем к выходу датчика подключены блок анализа медленноменяющейся амплитуды, который соединен через второй шифратор с запоминающим узлом, и блок отбора событий, выходы которого подключены к делителю частоты и двум вентилям, один из которых включен между тактовым генератором и формирователем тактовых серий, другой — между сумматором блока анализа медленноменяющейся амплитуды и блоком управления, который соединен с блоком отбора событий, вторым

5 шифратором, делителем частоты, сдвиговыми регистрами и ферритовым запоминающим узлом, который дополнительно соединен с выходами сдвиговых регистров и счетчиком.