Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

I) 407396

СОЮЗ |OBBTCHHX

Социалистических

Республик

М.Кл. G llс 19/00

Государственный комитет

Соавта Министров СССР по делам изобретений и открытий

УДК 681,327 (088,8) (72) Авторы изобретения С. А. Щербаков, В. Д. Паронджанов, В. И. Кузнецов и Б. g». Лукьянов (71) Заявитель (55) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

ОП ИС

ИЗОВРЕ

К АВТОРСКбму (61) Зависимое от авт. (22) Заявлено 28.08.72 с присоединением заявк (32) Приоритет—

Опубликовано 25.Х1.197

Дата опубликования оп

Предложенное изобретение относится к области вычислительной техники и может быть использовано при построении устройств хранения дискретной информации.

Известно буферное запоминающее устройство, содержащее регистры хранения чисел, логические элементы «И» и управляющий двухтактный регистр сдвига.

Основным недостатком известного устройства является необходимость наличия схем, вырабатывающих код адреса для управления устройством, и большое число элементов памяти, позволяющих хранить весь объем поступающей информации.

Целью изооретения является повышение плотности записи и упрощение известного буферного запоминающего устройства.

Поставленная цель достигается путем того, ITo нулевой выход каждого основного триггера управляющего регистра сдвига, кроме первого, подключен к элементу «И» предыдущего разряда этого регистра, а выход элемента «И» каждого разряда управляющего регистра сдвига соединен с пулевым входом вспомогательного триггера того же разряда, с единичным входом вспомогательного триггера последующего .разряда и со входами соответствующих элементов «И» регистров хранения чисел.

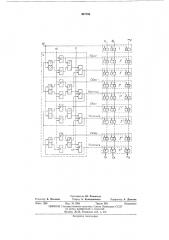

На чертеже изображена функциональная

2 схема предложенного буферного запоминающего устройства.

Устройство содержит элементы «И» 1, регистры 2 — 2" хранения m-разрядных чисел, соединенные через элементы «И» 8 — 8", у .:равляющий двуxTBKTnbIH регистр сдвига 1. включающий в себя о сно вныетригге ры 5 — 5", подключенные ко входам элементов «1!.

6 — б", и вспомогательные триггеры 7 — 7", 5п подключенные ко входам элементов «II»

8 — 8" и элементов «И» 9 — 9" .

Ко входам элементов «И» 8, 9 подключена шина 10 тактовых импульсов ТИ,. Ко входам элементов «И» 6 подключена шина 11 тактоBbIx импульсов ТИ . Ко входам элементов «И»

1 и вспомогательного триггера 7 подключен;1 шина 12 записи информации. Ко входу элемента «И» 6 подключена шина 18 считывания информации.

Предложенное устройство работает следующим образом.

На шину 10 тактовых импульсов ТИ и шину 11 тактовых импульсов ТИе постоянно поступают импульсы, сдвинутые один относи25 тельно другого, частота которых не ниже возможной частоты записи информации.

Для записи информации в запоминающсс устройство на шину 12 записи информации»оступает импульс, по которому через элементы

Зр «И» 1 первое т-разрядное слово записывается

407396

3 на регистр 2, одновременно вспомогательный триггер 7 управляющего регистра сдвига устанавливается в единичное состояние.

Первый импульс ТИ1 через элемент «И» 91 устанавливает в единичное состояние основной триггер 5 управляющего регистра сдвига.

Первый импульс ТИ через элемент «И» 6 устанавливает вспомогательный триггер 7 в нулевое состояние, а вопомогательный триггер 7 — в единичное и через элементы «И» 8 переписывает информацию из регистра 2 в регистр 2

Второй импульс ТИ1 через элемент «И» 9 устанавливает в единичное состояние основной триггер 5 управляющего регистра сдвига и через элемент «И» 8 устанавливает в нулевое состояние основной триггер 5 управляющего регистра сдвига, я также сбрасывает информацию в регистре 2 .

Второй импульс ТИг через элемент «И» 6 устанавливает вспомогательный триггер 7 в нулевое состояние, а вспомогательный триггер

7" — в единичное и через элемент «И» Р переписывает информацию из регистра 2 в ре> истр 23.

Через (а — 1) тактовых импульсов (где

il — количестго регистров для хранения чисел) riepvoc слово окажется в регистре 2".

Запись и перепись пз регистра B регистр с.чедующа.о слова осуществляются аналогично. 1ерез (n — 2) импульсов ТИ, и ТИ второе слово окажется в регистре 2"

При считывании информации пз запоминающего устройства на вход шины 18 считывания информации подается импульс и первое слово из регистра 2" через элементы «11» 8" выводится из устройства.

Первые же импульсы ТИ, и ТИ>, следующие за импульсом считывания, переписывают информацию из регистра 2" — в регистр 2" .

Аналогично переписывается информация из младших регистров в освобождающиеся регистры.

Таким образом, преимуществом предложенного устройства является то, что оно обеспечивает запись информации во все регистры

ip хранения чисел и последовательный сдвиг информации при считывании по сигналам записи и считывания с,помощью управляющего регистра без использования дешифратора адреса и устройств, формирующих код адреса.

Предмет изобретения

2о Буферное запоминающее устройство, содержащее регистры хранения чисел, одноименные разряды которых соединены последовательно через элементы «И», управляющий двухтакпный регистр сдвига, в каждом разря25 де которого основной и вспомогательный триггеры соединены через элементы «И», отличаюti!eecя тем, что, с целью повышения плотности записи и упрощения устройства, нулевой выход каждого основного триггера управляю5о щего регистра сдвига, кроме первого, подключен к элементу «И» предыдущего разряда этого регистра, а выход элемента «И» каждого разряда управляющего регистра сдвига соединен с нулевым входом вспомогательного триг35 гера того же разряда, с единичным входом вспомогательного триггера последующего разряда и со входамп соответствующих элементов

«И» регистров хранения чисел.

407396

/77 Р

) ! I !

3 и

I!!!! гарог!

I грелись р 2р

Редактор Б. Нанкина

Заказ 1224 Изд. № 1054 Тираж 564 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Загорская типография

I !

I ! ! ! ! !

I ! ! ! !

j ! и ! 8

Г;1 J !

Составитель Ю. Розенталь

Техред А. Камышникова Корректор А. Дзесова