Устройство ввода переменных коэффициентов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 408322-ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 13.1Х.1971 (№ 1696012/18-24) с присоединением заявки №

Приоритет

Опубликовано 10.XII.1973. Бюллетень № 47

Дата опубликования описания 22.IV.1974

М, Кл. G 06g 7/04

Государственный комитет

Совета Министров СССР ао делам изаоретений и открытий

УДК 681.337.1(088.8) Авторы изобретения А. Ф. Верлаиь, В. С. Годлевский, В. Г. Левитский и Г. И. Рачитский

Институт электродинамики АН Украинской ССР

Заявитель

УСТРОЙСТВО ВВОДА ПЕРЕМЕННЫХ КОЭФФИЦИЕНТОВ

Изобретение относится к области вычислительной техники.

Известны устройства ввода переменных коэффициентов, содержащие последовательно включенные первый и второй элементы задержки, входы и выходы которых соединены с тремя входами коммутатора, четвертый вход которого подключен к первому входу устройства, а выход соединен с первым входом элемента «И», и дешифратор, одни входы которого подключены ко второму входу устройства.

Все известные устройства требуют применения большого количества прецизионных электронных ключей.

Целью изобретения является упрощение устройства.

Предложенное устройство содержит блок записи ординат, входы которого подключены к третьему и четвертому входам устройства, а выходы соединены с другими входами дешифратора, блок памяти, вход которого подключен к первому выходу дешифратора и выходу элемента «И», а выход соединен со входом первого элемента задержки, блок задания наклона аппроксимирующего отрезка и изменения интервала между кодовыми импульсами, входы которого подключены к одному из выходов блока записи ординат, второму выходу дешифратора, выходу коммутатора, пятому и шестому входам устройства и выходу элемента «И», а выходы соединены с пятым входом коммутатора, вторым входом элемента «И» и входом время-импульсного множительного блока, второй вход которого подключен к седьмому входу устройства, а выход соединен с выходом устройства.

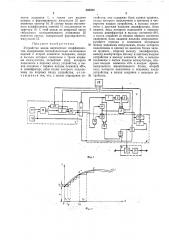

Блок-схема устройства приведена на фиг. 1.

Устройство содержит блок памяти 1 на маг10 нитострикционном элементе задержки, элементы задержки 2 и 3, элемент «И» 4, коммутатор 5, блок б задания наклона аппроксимирующего отрезка и изменения интервала между кодовыми импульсами, блок 7 записи

15 ординат, дешифратор 8 и время-импульсный множительный блок 9. Блок б содержит регистр 1О, счетчик импульсов 11, формирователь импульсов 12, элемент «И» 13, элемент

«ИЛИ» 14 и триггеры 15 и 16. Блок 7 записи

20 ординат содержит генератор 17 тактовых импульсов, генератор 18 импульсов цикла, коммутатор 19, счетчики 20 и 21 и элемент

«ИЛИ» 22. Время-импульсный множительный блок 9 содержит ключ 23 и сглаживающий

25 фильтр нижних частот 24.

Устройство работает следующим образом.

Пусть требуется ввести переменный коэффициент а(1), графическое изображение которого представлено на фиг. 2. Данная кривая

30 аппроксимируется ломаной ABC.... Каждый

408322

3 прямолинейный участок ломаной заменяется ступенчатой функцией, параметры которой выбирают из условий допустимой погрешности.

Значение ординаты в начальной точке А, а также значение ординат в узлах аппроксимации В, С, ... задаются цифровой частью гибридного вычислительного комплекса 25 и с помощью блока записи ординат 7 записываются в виде интервала времени т между двумя кодовыми импульсами в блоке памяти на магнитострикционном элементе задержки

1, где кодовые импульсы циркулируют по замкнутому контуру, поступая в течение каждого периода на триггер 16, который управляет работой ключа 23, Первый кодовый импульс дает команду на замыкание ключа 23, второй — на размыкание его. В результате на выходе ключа 23 образуется широтно-модулированная импульсная последовательность, которая поступает на сглаживающий фильтр нижних частот 24. Выходной сигнал фильтра в пределах допустимой погрешности представляет собой вводимую функцию а (t).

Сдвигая кодовые импульсы во времени друг относительно друга, можно изменять ширину импульсов, сформированных ключом 23, что эквивалентно изменению определенной ординаты вводимой функции a(t).

Ступенчатая функция на каждом из отрезков аппроксимации (АВ, ВС, ...) автоматически воспроизводится блоком 6 задания наклона аппроксимирующего отрезка и изменения интервала между кодовыми импульсами.

В регистр 10 и счетчик 11 записывается в обратном коде число широтно-модулированных импульсов п1 (фиг. 2), которое соответствует горизонтальной части ступеньки AD. Счетчик

11, отсчитав требуемое число импульсов и<, в момент времени 4 дает команды:

1) на запись этого же числа п1 из регистра

10 в счетчик 11 (регистр параллельного действия позволяет многократное считывание без его искажения);

2) на сдвиг в блоке памяти на магнитострикционном элементе задержки 1 кодовых импульсов друг относительно друга на величину Лт, что соответствует изменению ординаты у на величину by (фиг. 2).

Увеличение интервала времени на Лт между кодовыми импульсами достигается путем сдвига их в противоположные стороны на время Лт/2. Такой вид широтно-импульсной модуляции применяется для уменьшения постоянной составляющей погрешности, которая может возникать на выходе сглаживающего фильтра нижних частот 24, если в качестве последнего будет выступать интегратор, и которая обусловлена время-импульсной модуляцией.

Сдвиг кодовых импульсов на величину Лт осуществляется с помощью элементов задержки 2 и 3. При вводе постоянного коэффициента в аналоговую часть гибридного вычислительного комплекса кодовые импульсы цирку5

55 бО

65 лируют по замкнутому контуру, проходя через блок памяти на магнитострикционном элементе задержки 1 и элемент задержки 2.

При вводе переменного коэффициента с приходом команды от счетчика 11, в случае положительного приращения ординат, коммутатор 5 отключает элемент задержки 2 и первый кодовый импульс проходит на вход блока памяти на магнитострикционном элементе задержки 1 раньше во времени, чем при предыдущем цикле, на Лт/2. Затем коммутатор 5 подключает оба элемента задержки 2 и 3 и второй кодовый импульс задержится на время Лт/2. B результате за один цикл обращения кодовых импульсов интервал времени между ними увеличится на время Лт. После этого коммутатор 5 возвращает схему в исходное положение, при котором кодовые импульсы циркулируют по контуру через блок памяти на магнитострикционном элементе задержки 1 и элемент задержки 2 до прихода следующей команды счетчика 11.

В случае отрицательного приращения ординаты коммутатор 5 производит обратные переключения, в результате которых первый из кодовых импульсов проходит через оба элемента задержки 2 и 3 и задерживается на

Лт/2, а второй, минуя элементы задержки, проходит на время Лт/2 раньше.

В гибридном вычислительном комплексе блок записи ординат 7 является общим для всех устройств ввода переменных коэффициентов, поскольку в каждом устройстве работает эпизодически, записывая только начальные значения и значения ординат в узлах аппроксимации, Блок записи ординат 7 включается в состав требуемого устройства ввода переменных коэффициентов с помощью деш ифр атор а 8.

Перед записью нового значения ординаты стирается предыдущий код, циркулирующий по замкнутому контуру. При подаче команды на запись коммутатор 19 подключает генератор импульсов цикла 18 на вход триггера 15, который сработав, запирает элемент «И» 4 и отпирает элемент «И» 13. Элемент «И» 4 размыкает на время, равное одному периоду, контур блока памяти на магнитострикционном элементе задержки 1, и ранее записанные кодовые импульсы стираются. Элементы 13 и

14 обеспечивают прохождение стираемых кодовых импульсов на триггер 16 в течение периода стирания. Следующий импульс с генератора импульсов цикла 18 возвращает триггер 15, а следовательно, и элементы «И» 4 и

13 в исходное положение. Этот же импульс цикла дает команду на подключение генератора тактовых импульсов 17 к счетчикам 20 и 21. Счетчики 20 и 21, отсчитав требуемое число тактовых импульсов, дают команды на запись в блок памяти на магнитострикционном элементе задержки 1 соответственно двух кодовых импульсов.

Для синхронизации работы ключа 20 и блока памяти на магнитострикционном эле408322

Фиг.! менте задержки 1, а также для выдачи команд в формирователь импульсов 12 применяется триггер 16. В случае ввода постоянного коэффициента счетчик 11 отключается от триггера 16. С этой целью из цифровой части гибридного вычислительного комплекса 25 подается сигнал, запирающий формирователь импульсов 12.

Предмет изобретения

Устройство ввода переменных коэффициентов, содержащее последовательно включенные первый и второй элементы задержки, входы и выходы которых соединены с тремя входами коммутатора, четвертый вход которого подключен к первому входу устройства, а выход соединен с первым входом элемента «И», и дешифратор, одни входы которого подключены ко второму входу устройства, о т л ич а ю ще е с я тем, что, с целью упрощения ус6 тройства, оно содержит блок записи ординат, входы которого подключены к третьему и четвертому входам устройства, а выходы соединены с другими входами дешифратора, блок памяти, вход которого подключен к первому выходу дешифратора и выходу элемента «И», а выход соединен со входом первого элемента задержки, блок задания наклона аппроксимирующего отрезка и изменения интервала

10 между кодовыми импульсами, входы которого подключены к одному из выходов блока записи ординат, . второму выходу дешифратора, выходу коммутатора, пятому и шестому входам устройства и выходу элемента «И», а выходы

15 соединены с пятым входом коммутатора, вторым входом элемента «И» и входом времяимпульсного множительного блока, второй вход которого подключен к седьмому входу устройства, а выход соединен с выходом ус20 тройства.