Многочастотный дискриминатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №вЂ”

Заявлено 12.И I.1971 (№ 1679275/26-9) с присоединением заявки №вЂ”

Приоритет—

Опубликовано 10.XII. 1973, Бюллетень № 47

Дата опубликования описания 18Х1.1974.

М. Кл. Н 03d 3/04

Н 03k 9/06 тосударствениый аомитет

Совета Министров СССР ао делам изобретено» к отнятий

УДК 621.374.35 (088.8) Автор изобретения

В. М. Родионов

Заявитель

МНОГОЧАСТОТНЫЙ ДИСКРИМИНАТОР

Изобретение относится к радиотехнике и может быть использовано в системах частотной автоподстройки.

Известен многочастотный дискриминатор, содержащий преобразователь сигналов, вход которого через формирователь импульсов подсоединен к сигнальному входу устройства, один выход преобразователя подключен к счетной декаде непосредственно, а другой— через схему совпадения, дешифратор и интегратор, выполненный на двух аналоговых клгочах, выходы которых через резисторы подключены к интегрирующему элементу.

Однако известный многочастотный дискриминатор имеет недостаточные крутизну статической характеристики дискриминатора и диапазон частот.

Целью изобретения является расширение диапазона частот и повышение крутизны статической характерисгики дискриминатора.

Для этого первые пять выходных шин дешифратора объединены и подключены к управляющему входу одного аналогового ключа интегратора, шестая выходная шина дешифратора заземлена, остальные выходные шины дешифратора объединены и соединены с управляющим входом другого аналогового ключа интегратора.

Изобретение псяснено чертежами.

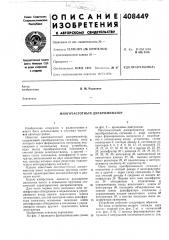

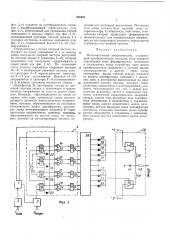

На фиг. 1 приведена функциональная схема; на фиг. 2 — временные диаграммы.

Многочастотный дискриминатор содержит преобразователь сигналов 1, вход которого через формирователь импульсов 2 подсоединен к сигнальному входу устройства, схему совпадения 8, счетную декаду 4, состоящую из триггеров 5, 6, 7, 8, 9, 10, 11, 12, вентилей 18, 14, 15, 16, 17, 18, 19, 20, 21 и диодов 22, 28, 24, 25, дешифратор 26 с диодами 27, 28, 29, 80, 31, 1п 32, 88, 34, 85, интегратор 86, выполненный на аналоговых ключах 87, 38, выходы которых через резисторы 89, 40 подключены к интегрирующему элементу 41, и резистор 42.

Один выход преобразователя сигналов 1

15 подключен к счетной декаде 4 непосредственно, а другой — через схему совпадения 8. Выход счетной декады 4 соединен со входом дешифратора 26. Первые пять шин дешифратора 26 объединены и подключены к управляющему входу аналогового ключа 87 интегратора 86, последние объединенные выходные шины дешифратора соединены с управляющим входом аналогового ключа 38 интегратора 86, а шестая выходная шина де2Б шифратора заземлена.

Устройство работает следующим образом.

На вход устройства подают сигналы двух частот: опорной (см. фиг. 2 а) и сигнальной (см. фиг. 2 б). С выхода формирователя им30 пульсов 2 импульсная последовательность (см.

408449 опора сигв фиг. 2 в) подается на преобразователь сигналов 1, вырабатывающий строб-импульс (см. фиг. 2 г), необходимый для управления схемой совпадения 3, импульс сброса (см. фиг. 2 д), возвращающий триггеры счетной декады 4 в исходное состояние, и импульс перезаписи (см. фиг. 2 е), открывающий вентили 14 — 21 счетной декады 4.

Строб-импульс и сигнал опорной частоты поступают на схему совпадения 8, с ее выхода Ip пачки импульсов опорной частоты поступают на счетную декаду 4 (триггеры 5 — 8), которая производит счет импульсов, содержащихся в одной пачке (см. фиг. 2 ж). По окончании счета импульс перезаписи открывает вентили

14 — 21 и комбинация двоичной системы записи триггеров 5 — 8 переписывается триггерами 9 — 12 для запоминания. Вентили 14 — 21 закрываются, а триггеры 5 — 8 устанавливаются в исходное состояние импульсом сброса. 2р

Дешифратор 2б преобразует сигнал из двоичной системы записи в десятичную и выдает импульс напряжения на одну из десяти своих шин. Команда, образовавшаяся на одной из первых пяти шин, производят заряд интегри- 25 рующего элемента положительным напряжением; команда, образовавшаяся на последних объединенных шинах дешифратора, производит заряд интегрирующего элемента 41 отрицательным напряжением; наконец, команда, zp образовавшаяся на шестой шине, не оказывает влияния на интегрирующий элемент, сохраняя его потенциал неизменным. Потенциал этой шины соответствует нулевой точке дискриминатора. Стабильность этой точки, QTHQсительно которой происходит формирование положительного или отрицательного напряжения на интегрирующем элементе, определяется стабильностью опорной частоты.

Предмет изобретения

Многочастотный дискриминатор, содержащий преобразователь сигналов, вход которого подсоединен через формирователь импульсов к сигнальному входу устройства, один выход преобразователя подключен к счетной декаде непосредственно, а другой — через схему совпадения, выход счетной декады соединен со входом дешифратора, имеющего и выходных шин, и интегратор, выполненный на двух аналоговых ключах, выходы которых через резисторы подключены к интегрирующему элементу, отличаюсцийся тем, что, с целью расширения диапазона частот и повышения крутизны статической характеристики дискриминатора, первые пять выходных шин дешифратора объединены и подключены к управляющему входу одного аналогового ключа инте-. гратора, шестая выходная шина дешифратора заземлена, остальные выходные шины дешифратора объединены и соединены с управляющим входом другого аналогового ключа интегратора а.

408449

Р 5631М %3аа131 )) Г (e) Фиг 2

Составитель Г. Челей

Техред T. Ускова

Редактор А. Зиньковский

Корректор Н. Аук

Типография № 24 Союзполиграфпрома, Москва, 121019, ул. Маркса — Энгельса, 14

Заказ 179 Изд. № 320 Тираж 768 Подписное

ЦНИИПИ Государственного комитета Совета Мйнистров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5