Одноразрядный сумм.а^тор

Иллюстрации

Показать всеРеферат

СОЮЗНО ЛТ:;. ь; . I", )(;ÙÙ;;,, библиотена!

40938I

Союз Советских

Социалистииескик

Республик

ОП И

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства ¹â€”

Заявлено 21.1.1972 (№ 1741684/26-9) с присоединением за)явки №вЂ”

Приоритет—

Опубликовано ЗО,Х!.1973. Б!оллетень № 48

Дата опубликования описания 26.1Х.74

М.Кл. Н 03k 19/08

Гоеудорстввнный ноинтот

Советв Мнннотроо СССР оо делам нэебретйннй н откро)тнй

УДК 621.374.32 (088.8) Авторы изобретения

П. В. Сивобород и Г. В. Дитвинский

Заявитель

ОДНОРАЗРЯДНЫИ СУММАТОР

)I =On !In -, аул —,— Cn трет»» каскад

"е

) - адвл-- адвц- -вд . l, 20

11= (в +в„!)аи — в„в„

Изобрете»11С от»оснтся к области радиотехники.

Известные сумматоры на МДП-транзисторах, построенные»а логическ!11х элементах с потенциальной структурой, не обладают значительным быстродействием, и при их использовании в последовательных арифметических устройствах требуется элемент задержки в цепи переноса информации в старший разряд.

Известны логические элементы и элементы памяти на ЧДП-транзисторах, отличающиес51 значительным быстродсйств»см и позволяющие построить быстродействующие логические устройства. Но, поскольку система управляется синхро»изиру1ощнми импульса ми, сумматор, выполненный на указанных элеме»тах, реализует операцию сложения (пере»оса) за время, превышающее два такта илп равное им. Это в конечном счете уменьшает общее быстродействие по крайней мере в два раза. Повысить быстродействие можно, сократив число тактов, за которое реализуется опе;.)1)ция сложения, до одного.

С целью повышения быстродействия в предлагаемоAI cс.у )мIiм Iа тTоoр !е в»bы)х оoд lы логических схем для образования суммы соединены с нулевыми плечами триггера суммы, а выход логической схемы образования пере:!оса соединен с нулевым плечом триггера переноса.

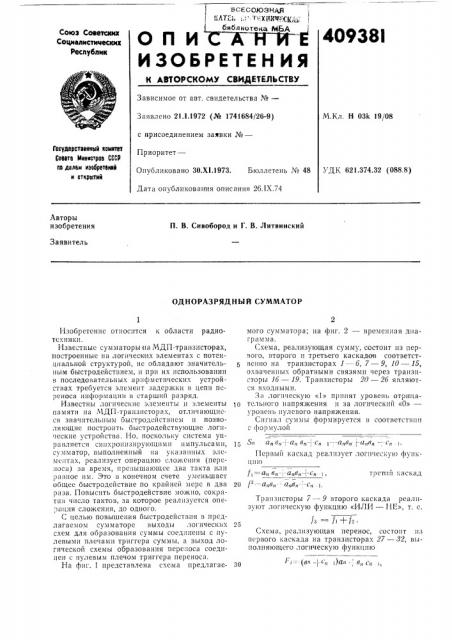

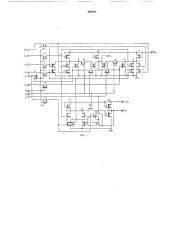

На фиг. 1 представлена схема предлагаемого сумматора; на фиг. 2 — временная диаграмма.

Схема, реализующая сумму, состоит из первого, второго и третьего каскадов соответствс»но на транзисторах 1 — 6, 7 — 9, 10 — 15, охвачен»ых обратными связями через тра»зисторы 16 — 19. Транзисторы 20 — 26 являютC5I ВХОДНЫМИ.

За логическую «1» принят уровень отрпца$0 тельного напряжения и за логический «0»вЂ” уровень нулевого напряжения.

Сигнал суммы формируется в соответствии с <1) о р мул о !1 (5 а„в„-, -а„в„= ;-с„!в --- а,в„ l-а,в, —;-!, Первы!! каскад реализvет:1огнческу1!) !1)ункцшо

Транзисторы 7 — 9 второго каскада реализуют логическую функцию «ИЛИ вЂ” НЕ», т. с.

fa = f1+a

Схема, реализующая перенос, состоит»з первого каскада на транзисторах 27 — 82, выполняющего логическую функцию

409381 и второго каскада на транзисторах 88 и 84, выполняющего роль инвертора.

Транзисторы 85 — 87 выполняют функцию управляемых обратных связей. Реализация переноса осуществляется в соответствии с формулои

cn = (в» + с, l) а, +в с»

Работа схемы- осуществляется в соответствии с таблицей истинности. в» с„| .з» а»

О О

1 О

1 О

О 1

1 О

О Х

0 1

1 1

О

О

1

О

О

О

О

О

0

В качестве примера рассмотрена работа сумматора, когда а„= 1, Ь, = l, с = 1.

Предположим, что в исходном состоянии, до начала рабочего такта, напряжение на выходах схемы равно нулю, т. е. 5, О и С» — 0, Под тактом понимается время действия импульсов yi y2 cps, причем импульс ip меньше по длительности и подан в противофазе импульсам q;2, rg3.

При подаче на схему тактовых импульсов транзисторы 16 — 19, 85 — 87 запираются, что приводит к отключению обратных связей между каскадами.

Напряжения с входов через открытые транзисторы 20 — 2б поступают на входы схем формирования сигналов $, .и С, .

Поскольку транзисторы б, 11 и 12 открыты, то напряжение на выходе первого и второго каскадов равно нулю. В конце первого такта транзисторы lб и 19 открываются, что приводит к подаче логического «О» на затворы транзисторов 7 и 9. Транзисторы 7 и 9 закрываются. Это обеспечивается «1» на выходе S»,ò. е.

5 " n = 1.

Открытые транзисторы 28 — 82 обеспечивают нулевое напряжение на выходе первого каскада схемы формирования переноса. В конце первого такта открывается транзистор 85, и нулевое напряжение с первого, каскада передается на транзистор 84, что приводит к

С„= 1. На временной диаграмме по второму. такту реализуется сумма и перенос, когда а» =О, Ь„=О,с„ =О.

15 При других комбинациях входных сигналов работа схемы аналогична.

При необходимости выходные, и входные сигналы могут быть проинвертированы обычным инвертором. м При соответствующей коммутации переменой а» на а., на входе схемы формирования переноса сумматор выполняет функцию вычитателя.

Предлагаемый одноразрядный сумматор реализован на МДП-транзисторах, его можно выполнить в виде полупроводниковой интегральной микросхемы.

Предмет изобретения

Одноразрядный сумматор на МДП-транзисторах, содержащий две логические схемы для образования суммы, логическую схему образования переноса, два триггера суммы и триг35 гер переноса, отличающийся тем, что, с целью повышения быстродействия, выходы логических схем для образования суммы соединены с нулевыми плечам|и триггера суммы, а выход логической схемы образова|ния переноса сое40 ди нен с нулевым плечом триггера переноса.

40938 !

СЕ)-т с,, Составитель А. Ходаков

Тскред 3. Тараненко

Редактор F. Караулова

Корректор Н. Ауи

Заказ 1806

11зд. ¹ 1111 Тираж 768

III IHHIIII Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская иаб.,;l. 4/5

Подписное

Обл. тии. 1,остромского управления издательств, полиграфии. и книжной. торговгш