Патент ссср 411652

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 4И652

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 30.111.1972 (№ 1765803/26-9) с присоединением заявки №

Приоритет

Опубликовано 15.1.1974. Бкллетень № 2

Дата опубликования описания 27Х.1974

М. Кл. Н 03k 25/00

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий

УДК 681.326.07(088,8) Авторы изобретения

В. И. Вешняков и В, И. Корнейчук

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции

Заявитель

БУФЕРНЫЙ НАКОПИТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано, например, для управления производством.

Известен буферный накопитель, содержащий регистры сдвига, входной регистр, коммутатор, вход которого через схему «И» соединен с генератором импульсов и триггером, один установочный вход последнего подключен к выходу схемы «ИЛИ», а другой — к схеме запрета, и схемы совпадения.

С целью упрощения буферного накопителя регистры сдвига выполнены на потенциальных однотактных триггерах, причем прямой и инверсный выходы каждого i — 1 триггера регистра сдвига соединены с одними входами схем совпадения, выходы которых подключены к раздельным входам i-го триггера, а другие входы этих схем совпадения соединены с i-ым входом коммутатора.

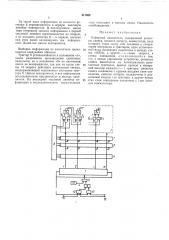

На чертеже приведена структурная схема предлагаемого буферного накопителя.

Накопитель состоит из регистров 1 — 4, в которых потенциальные однотактные триггеры

5>... 5 соединены через схемы совпадения 6ь..

6, коммутатора 7, входного регистра 8, прямые и инверсные выходы которого попарно соединены со схемами совпадения 6ь.. б„, подключенными к раздельным входам триггеров

51... 5, образующих первую числовую линейку.

Коммутатор 7 представляет собой сдвиговый кольцевой регистр, каждый i-й разрядный выход которого со вторыми входами схем совпадения 6,... б„, подключенный к раздельным входам триггеров 5ь.. 5„, образующих i-ю числовую линейку (i изменяется от 1 до т, где т — полная емкость накопителя). Триггер

9 и генератор 10 подключены к схеме «И» 11, выход которой подключен ко входу коммута10 тора 7.

Один установочный вход триггера 9 подключен к выходу схемы «ИЛИ» 12, а другой — к схеме 13 запрета. К схеме «ИЛИ» 12 подключены клеммы 14 «запись» и клеммы 15 «вы15 борка».

Буферный накопитель работает следующим образом.

При записи информации из входного регистра 8 в буферный накопитель от клеммы 14

20 «запись» производится переключение триггера 9 из положения «О» в положение «1», что дает разрешение на прохождение сдвиговых импульсов от генератора 10. В начальном состоянии в регистрах 1 — 4 находится одна «1»

25 в т-разряде. При действии сдвиговых импульсов эта «1» «пробегает» последовательно по всему регистру и вновь заносится из первого разряда в т-й, устанавливая при этом соответствующий триггер 5ь.. 5„в «нулевое» со30 стояние. Цикл заканчивается.

411652

За такой цикл информация из входного регистра 8 переписывается в первую числовую линейку накопителя. В последующем цикле (при очередной записи) информация с первой числовой линейки переписывается во вторую, а из входного регистра 8 — в первую, погасив при этом ранее находящуюся там информацию. Далее все циклы повторяются.

Выборка информации из накопителя производится следующим образом.

Триггер 9 устанавливается в положение «1», давая разрешение прохождению сдвиговых импульсов, но в положение «0» по окончании цикла не возвращается, так как на входе схемы 13 запрета действует длительный сигнал, поддерживающий «единичное» состояние триггера 9. Циклы повторяются, и вся информация последовательно продвигается к выходу накопителя. Из последней числовой линейки информация в последовательном параллельном коде поступает в каналы связи. Накопитель освобождается.

Предмет изобретения

Буферный накопитель, содержащий регистры сдвига, входной регистр, коммутатор, вход которого через схему «И» соединен с генератором импульсов и триггером, один установоч1р ный вход последнего подключен к выходу схемы «ИЛИ», а другой — к схеме запрета, и схемы совпадения, отличающийся тем, что, с целью упрощения устройства, регистры сдвига выполнены на потенциальных одно15 тактных триггерах, причем прямой и инверсный выходы каждого L — 1 триггера регистра сдвига соединены с одними входами схем совпадения, выходы которых подключены к раздельным входам 1-го триггера, а другие входы

20 этих схем совпадения соединены с -ым выходом коммутатора.