Патент ссср 412604

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Соцыолисткческмх

Республик

Зависимое от авт. свидетельства №вЂ”

Заявлено 02.Ч!!1.1971 (№ 1687937/18-24) с присоединением заявки №вЂ”

Приоритет—

Опубликовано 25.11974. Бюллетень ¹ 3

Дата опубликования описания 11.Х1,1974

М. Кл. G 06t 9/16

Государственныи комитет

Совета Министров СССР по делам изобретений и открытий

УДК 681.326 (088 8) Авторы изобретения

Заявитель

А. К. Баумс, У. Я. Грунде и У. Ю. Эрглис

Институт электроники и вычислительной техники

АН Латвийской ССР

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к цифровой вычислительной технике и предназначено для использования в устройствах управления цифровых вычислительных машин.

Известны микропрограммные устройства управления, содержащие основной и дополнительный блоки адресаций, связанные с блоком управления и первым накопителем микрокоманд. Однако эти устройства отличаются малым быстродействием.

Цель предлагаемого изобретения — повышение быстродействия устройства.

Для этого оно содержит схему тождественности и второй накопитель микрокоманд, входы каждого накопителя соединены с основным блоком адресаций, связанным со схемой тождественности, которая соединена с дополнительным блоком адресаций и блоком управления.

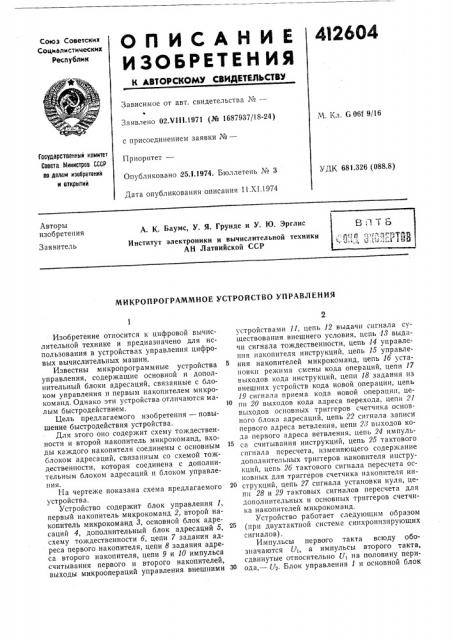

На чертеже показана схема предлагаемого устройства.

Устройство содержит блок управления 1, первый накопитель микрокоманд 2, второй накопитель микрокоманд 8, основной блок адресаций 4, дополнительный блок адресаций 5, схему тождественности б, цепи 7 задания адреса первого накопителя, цепи 8 задания адреса второго накопителя, цепи 9 и 10 импульса считывания первого и второго накопителей, выходы микроопераций управления внешними устройствами 11, цепь 12 выдачи сигнала сушествования внешнего условия, цспь 13 выдачи сигнала тождественности, цепь 14 управления накопителя инструкций, цепь 15 управления накопителей микрокоманд, цепь lб установки режима смены кода операций, цепи 17 выходов кода инструкций, цепи 18 задания из внешних устройств кода новой операции, цепь

19 сигнала приема кода новой операции, цепи 20 выходов кода адреса перехода, цепи 21 выходов основных триггеров счетчика основного блока адресаций, цепь 22 сигнала записи первого адреса ветвления, цепи 23 выходов кода первого адреса ветвления, цепь 24 импульса считывания инструкций, цепь 25 тактового сигнала пересчета, изменяющего содержание дополнительных триггеров накопителя инструкций, цепь 2б тактового сигнала пересчета основных для триггеров счетчика накопителя инструкций, цепь 27 сигнала установки нуля, цепи 28 и 29 тактовых сигналов пересчета для дополнительных и основных триггеров счетчика накопителей микрокоманд.

Устройство работает следующим образом (при двухтактной системе синхронизирующих сигналов) .

Импульсы первого такта всюду обозначаются Ь ь а импульсы второго такта, сдвинутые относительно U, на половину периода,— У . Блок управления 1 и основной блок

412604

1з + foe

65 адресаций 4 осуществляют последовательную выборку микрокоманд из накопителей .микрокоманд по цепям 9, 10 и 7, 8 соответственно.

Одновременно схема тождественности б сравнивает текущий очередной адрес выборки микрокоманд с адресной частью инструкции, поступающей из дополнительного блока адресаций 5. В случае их совпадения схема тождественности б засылает сигнал в блок управления

1, который прекращает выборку микрокоманд и разрешает засылку адресов (определяющих новую ветвь микропрограммы) из дополнительного блока адресаций 5 в основной блок адресаций 4. При несовпадении адресов порядок выборки микрокоманд не изменяется. Система адресаций построена таким образом, что без необходимости пропуска микротактов в местах разветвления микропрограмм обеспечивается образование адресов микрокоманд с частотой в два раза большей, чем где /зу — время задержки сигналов микроопераций на выходах ЗУ относительно момента подачи сигнала считывания соответствующей микрокоманды; — время выполнения микрооперации переадресации.

Микрокоманды считываются попеременно с первого 2 и второго 8 накопителей, причем импульс считывания на один накопитель подается до того, как появляются сигналы микрокоманды на выходе дpyroro на копителя.

Импульс последующего считывания должен подаваться на один и тот же накопитель только после того, как сигналы, соответствующие предшествующей считываемой с этого накопителя микрокоманде, реализовали необходимые микрооперации. Поэтому частота считывания микрокоманд в предлагаемом устройстве

Адресацию неразветвленых частей микропрограмм осуществляет основной блок адресаций, построенный в виде двухтактного счетчика. При этом одновременно с подачей импульса считывания на первый накопитель (по цепи

9) импульсом того же такта производителя переадресация триггеров счетчика, связанных со вторым накопителем, и наоборот. Так как задание адреса последующей микрокоманды происходит без участия выходов накопителей, частота считывания микрокоманд не должна только превышать частоту работы счетчика.

Адресацию микрокоманд в местах разветвления микропрограмм, а также ожидания в определенных местах микропрограмм обеспечивает дополнительный блок адресаций 5, получающий тактирующие импульсы из блока управления 1 (по цепям 14). При этом реализуются

55 особые инструкции, фиксированные в накопителе инструкций блока 5. Так как в микропрограммах распространенного типа условных переходов и прерываний значительно меньше, чем безусловных переходов от микрокоманды к микрокоманде, требуемая емкость накопителей инструкций намного (в 5 — 10 раз) меньше, чем общая ейкость накопителей микрокоманд.

Для считывания инструкций с накопителя служит тактовый импульс У (поступающий по цепи 24), как только в блоке управления 1 образуется сигнал, что предшествующая инструкция реализована. Инструкции реализуются (при наличии сигнала о необходимости реализации инструкции) импульсом (1 . Инструкция содержит всю необходимую информацию для определения момента ее выполнения, информацию для осуществления при ее реализации условной переадресации или установки начала ожидания и выхода из ожидания. Основная идея, заложенная в основу построения дополнительного блока адресаций 5 и блока управления 1, состоит в том, что момент выполнения инструкции (а следовательно, такт условной переадресации или такты ожидания) определяется пе сигналами микроопераций на выходах 11 накопителей микрокоманд, а адресом микрокоманды, содержащимся в основных триггерах счетчика основного блока адресаций 4. Этот адрес сопоставляется схемой тождественности б с адресом перехода инструкции, подготовленной для реализации в блоке 5, Командой начала реализации инструкции является сигнал тождественности в цепи 18, выдаваемый схемой тождественности.

Переход на новую выполняемую операцию вызывается сигналом микрооперации приема кода новой операции, подаваемым с одного выхода второго накопителя микрокоманд 3 по цепям

19 и 1б. Этот сигнал подается после реализации микропрограммы текущей операции и по цепи 18 засылает код новой операции из внешних устройств, а по цепи 1б устанавливает в блоке управления:1 режим смены кода операции. В режиме смены кода операции с помощью импульса У, (по цепи 24) считывается инструкция, адресом которой является новый код операции. Эта инструкция содержит только первый и второй адреса ветвления, которые импульсом U в режиме смены операции засылаются соответственно в дополнительные триггеры счетчика блока 4 (сигнал по цепи 22) и дополнительные триггеры счетчика блока 5 (сигнал по цепи ЗО). Одновременно с этой засылкой в блоке управления 1 режим смены кода операции прекращается.

Предмет изобретения

Микропрограммное устройство управления, содержащее основной и дополнительный блоки адресаций, связанные с блоком управления и первым накопителем микрокоманд, отличаюи ееся тем, что, с целью повышения оыстродействия устройства, оно содержит схему тож412604 схемой тождественности, которая соединена с дополнительным блоком адресаций и блоком управления.

Составитель В. Казаков

Техред Е, Борисова

Корректор Т. Хворова

Редактор Н. Козлова

Заказ 1203/193 Изд. № 390 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

Москва, %-35, Раушская наб., д. 4/5

Тип. Харьк. фпл. пред. «Патент». дественности и второй накопитель микрокоманд, входы каждого накопителя соединены с основным блоком адресаций, связанным со

2б