Патент ссср 416877

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 4I6877

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВНДЕТЕЙЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹â€”

hl. Кл. Н 03k 19/08

Заявлено 20Х1.1972 (№ 1798402/26-9) с присоединением заявки №вЂ”

Приоритет

Опубликовано 25.11.1974. Бюллетень № 7

Дата опубликования описания 26Х1.1974

Государственный номнтет

Совета Министров СССР по делам изаоретений и отнрытий

УД1 681.32.001(088.8) Авторы изобретения С. А. Моралев, В. П. Сидоренко, А. Я. Сирота и Ю. В. Таякин

Заявитель

ИНВЕРТОР НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к радиотехническим устройствам, в частности к элементам

МОП вЂ” ИС и может быть использовано в цифровой вычислительной технике.

Известен инвертор на МДП-транзисторах, содержащий последовательно включенные инвертирующий и нагрузочный транзисторы, конденсатор, первый вывод которого через зарядный транзистор подключен к шине питания, разрядный и дополнительный транзисторы.

Цель изобретения — повышение быстродействия и нагрузочной способности устройства.

Для этого первый вывод конденсатора соединен с затвором нагрузочного транзистора, исток которого через дополнительный транзистор соединен со стоком разрядного транзистора и вторым выводом конденсатора, причем затворы разрядного и дополнительного транзисторов соединены соответственно с первой и второй шинами тактовых импульсов.

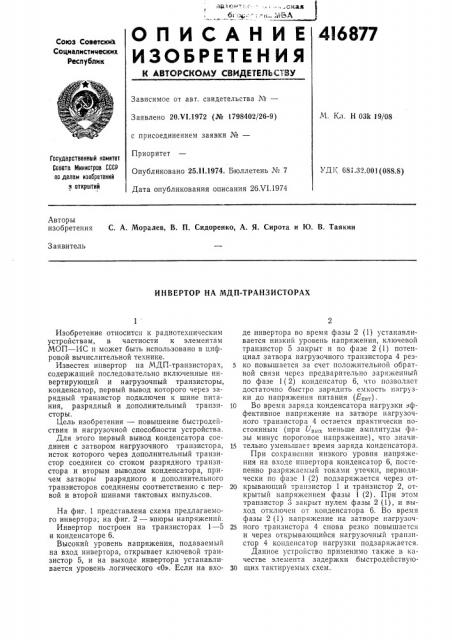

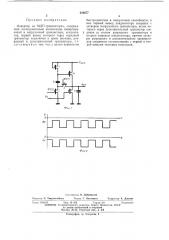

На фиг. 1 представлена схема предлагаемого инвертора; на фиг. 2 — эпюры напряжений.

Инвертор построен на транзисторах 1 — 5 и конденсаторе 6.

Высокий уровень напряжения, подаваемый на вход инвертора, открывает ключевой транзистор 5, и на выходе инвертора устанавливается уровень логического «О». Если на входе инвертора во время фазы 2 (1) устанавливается низкий уровень напряжения, ключевой транзистор 5 закрыт и по фазе 2 (1) потенциал затвора нагрузочного транзистора 4 рез5 ко повышается за счет положительной обратной связи через предварительно заряженный по фазе 1(2) конденсатор 6, что позволяет достаточно быстро зарядить емкость нагрузки до напряжения питания (Е „,).

10 Во время заряда конденсатора нагрузки эффективное напряжение на затворе нагрузочного транзистора 4 остается практически постоянным (при У„,, меньше амплитуды фазы минус пороговое напряжение), что значи1ь тельно уменьшает время заряда конденсатора.

При сохранении низкого уровня напряжения на входе инвертора конденсатор 6, постепенно разряжаемый токами утечки, периодически по фазе 1 (2) подзаряжается через от20 крывающий транзистор 1 и транзистор 2, открытый напряжением фазы 1 (2). При этом транзистор 3 закрыт нулем фазы 2 (1), и выход отключен от конденсатора 6. Во время фазы 2 (1) напряжение на затворе нагрузоч25 ного транзистора 4 снова резко повышается и через открывающийся нагрузочный транзистор 4 конденсатор нагрузки подзаряжается.

Данное устройство применимо также в качестве элемента задержки быстродействуюЗО щих тактируемых схем.

416877

Предмет изобретения

Фиг 1

V а

Фиг 2

Составитель И. Дубровский

Редактор 3, Твердохлебова Техред Г, Васильева

Корректор А. Дзесова

Заказ 1824/1б Изд. № 502 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр Сапунова, 2

Инвертор на МДП-транзисторах, содержащий последовательно включенные инвертирующий и нагрузочный транзисторы, конденсатор, первый вывод которого через зарядный транзистор подключен к шине питания, разрядный и дополнительный транзисторы, отл и ч а ю щи и с я тем, что, с целью повышения быстродействия и нагрузочной способности, в нем первый вывод конденсатора соединен с затвором нагрузочного транзистора, исток которого через дополнительный транзистор соединен со стоком разрядного транзистора и вторым выводом конденсатора, причем затворы разрядного и дополнительного транзисторов соединены соответственно с первой и второй шинами тактовых импульсов.