Патент ссср 417800

Иллюстрации

Показать всеРеферат

с.

"к I

4Г860

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских . Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 17.Х1.1972 (№ 1846979/18-24) с присоединением заявки №

Приоритет

Опубликовано 28.11.1974. Бюллетени ЛЪ 8

Дата опубликования описания 9Л 11.1974

М. Кл. 6 06g 7/40

Гаоударотаенный комитет

Соната Министров СССР аа делам изобретений

- н открытий

УДК 681.333(088.8) Авторы изобретения

В. П. Емелин, А. Т. Лукьянов и Г. О. Розенфельд

Казахский ордена Трудового Красного Знамени государственный университет им. С. М. Кирова

Заявитель

УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ

УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ

Изобретение относится к области аналогоцифровой вычислительной техники и может быть использовано для решения дифференциальных уравнений в частных производных.

Известны устройства для решения дифференциальных уравнений с автоматической регистрацией результатов, содержащие сетку омических резисторов, систему переключателей и многоточечный автоматический самопишущий прибор, измерительная часть которого выполнена по мостовой компенсационной схеме, составленной из реохорда и потенциометров питания сетки.

Однако эти устройства не пригодны для решения ряда задач, где требуется в процессе решения автоматически регулировать величину сопротивления резисторов сетки в зависимости от величины напряжения в ее узлах, дают низкую точность при решении других задач и требуют остановок для ручной настройки потенциометров питания сетки, т. е. не являются полностью автоматическими.

Цель изобретения — расширение класса решаемых задач, повышение точности решения и полная автоматизация устройства.

В предлагаемом устройстве эта цель достигается путем применения сетки с цифровыми управляемыми резисторами, блока управления, аналогового функционального блока, преобразователя аналог — код, блоков коммутации и блока памяти.

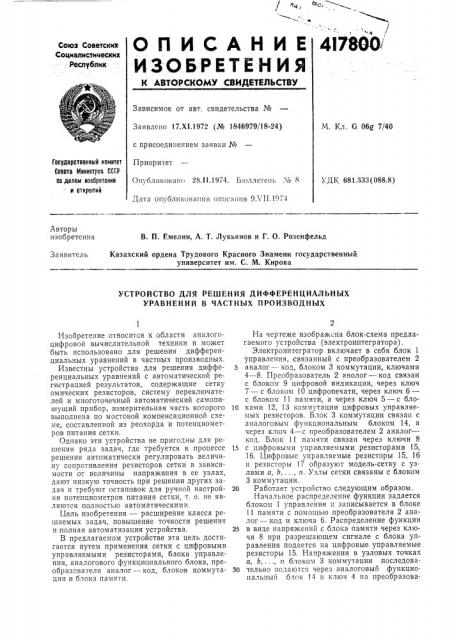

На чертеже изображена блок-схема предлагаемого устройства (электроинтегратора) .

Электроинтегратор включает в себя блок 1 управления, связанный с преобразователем 2 аналог — код, блоком 3 коммутации, ключами

4 — 8. Преобразователь 2 анолог — код связан с блоком 9 цифровой индикации, через ключ

7 — с блоком 10 цифропечати, через ключ 6— с блоком 11 памяти, а через ключ 5 — с бло10 ками 12, 13 коммутации цифровых управляемых резисторов. Блок 3 коммутации связан с аналоговым функциональным блоком 14, а через ключ 4 — с преобразователем 2 аналог— код. Блок 11 памяти связан через ключи 8

15 с цифровыми управляемыми резисторами 15, 16. Цифровые управляемые резисторы 15, 16 и резисторы 17 образуют модель-сетку с узлами а, b,..., и. Узлы сетки связаны с блоком

3 коммутации.

20 Работает устройство следующим образом.

Начальное распределение функции задается блоком 1 управления и записывается в блоке

11 памяти с помощью преобразователя 2 аналог — код и ключа 6. Распределение функции

25 в виде напряжений с блока памяти через ключи 8 при разрешающем сигнале с блока управления подается на цифровые управляемые резисторы 15. Напряжения в узловых точках а, b,..., и блоком 3 коммутации последова30 тельно подаются через аналоговый функциональный блок 14 и ключ 4 па преобразователь 2 аналог — код. Сигналы, с преобразователя 2 через ключ 5 подаются на блок 13 коммутации, который последовательно подключает цифровые управляемые резисторы 16 к преобразователю 2.

Сигналы с преобразователя 2 выставляют значения сопротивлений цифровых управляемых резисторов 16 как функцию напряжений в узлах а, b,..., n, снимаемых блоком 3 коммутации, работгнощим синхронно с блоком 13 н аналоговым функциональным блоком 14.

После этого по команде с блока управления ключи 8 отключают от блока памяти цифровые управляемыс резисторы 15 и подключают резисторы 17. Цикл, повторяется с той разницей, что теперь как функцию напряжения в узлах выставляются сопротивления цифровых управляемых резисторов 15. Циклы повторяются до тех пор, пока напряжения в узлах а, К..., n не перестанут изменяться; при этом по сигналу с блока 3 коммутации блок управления отключает аналоговый функциональный блок 14 от преобразователя 2, а напряжения в узлах а, b,..., n через ключ 4, преобразователь 2, ключ 7 подаются на блок 10 цифропсчати, на блок 9 индикации, а через ключ 6 записываются в блоке 11 памяти. Далее циклы повторяются, только с новым распределением функции.

Предмет изобретения

Устройство дл решения дифференциальных уравнений в частных производных, содержа5

30 щее модель-сетку, узлы которой подключены к первому блоку коммутации, первым выходом соединенному с первым входом блока управления, выходы которого подключены к первым входам соответствующих ключей и к входу первого блока коммутации, блок памяти, одна группа выходов которого соединена с моделью-сеткой, второй и третий блоки коммутации и блок индикации, о т л и ч а ю щ е сся тем, что, с целью расширения класса решаемых задач, оно содержит аналоговый функциональный блок, вход которого подключен к второму выходу первого блока коммутации, а выход соединен с вторым входом первого ключа, третий вход которого подключен к второму выходу псрвого блока коммутации, преобразователь аналог — код, вход которого соединен с выходом первого ключа и с вторым входом блока управления, а выход подключен к второму входу второго ключа, выходы которого соединены с входами второго и третьего блоков коммутации, третий вход блока управления подключен к вторым входам треч ьего и че i вертого ключей и к блоку индикации, причем выход четвертого ключа соеди,нен с входом блока памяти, а модель-сетка дополнительно содержит цифровые управляемые резисторы, соединенные с узлами моделисетки и подключенные к выходам второго и третьего блоков коммутации и к выходам соответствующих ключей, входы которых соединены с другой группой выходов блока памяти.

Составитель Е. 1имохииа ! сдактор И. Орлова Техре. Е. Борисова Корректор Е. Сапу инва

=> о;;. s !647jl! !1зд. Ы !323 Тпракк 624 Г!одписнс

1!! .! 1ИПИ Государстве ного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-З5, Раушская наб., д. 4/5

Типографии, пр. Сапунова, 2