Патент ссср 418864

Иллюстрации

Показать всеРеферат

ЯЕ g 1ф4Е ИЕРЕЕ ииитен " ""„.,„,, „.:-. @скееив б,л, МОЛЛ

Оков Советсккл

1 ОЦМаниетИчЕЕКМ

Респуопик

Зависимое от авт. свндс:сльс".ва ¹â€”

М. 1хл. б 06j 1,/02

Заявлено 17,VII.1972 (№ 1817238/! 8-,) с присоединением заявки . гав

Приоритет

Опубликовано 05.111.1974. Бюллетень № 9

Дата опубликования описания 26л 11.1974

Государственный комитет

Соната 1иинистров СССР ао делам изаоретений и открытий Д1х 081.335.7(088.8) Авторы изобретения

Ю. В. Чернухин, И. Д. Скролис и О. Б. Макаревич

Таганрогский радиотехнический институт

Заявитель

ЦИФРОВОЙ ИНТЕГРАТОР

Изобретение относится к области вычислительной техники и может быть использовано при конструировании и разработке цифровых интегрирующих машин и структур.

Известны цифровые интеграторы с одноразрядными приращениями, содержащие нерзьш сумматор, параллельно которому подклю-Ieii регистр подынтегральной функции, выходом соединенный через схему умножения на один разряд со вторым сумматором, параллельно которому подключен регистр остатков, выходом соединенный с выходным устройством, имеющим выход одноразрядных приращений.

Схема умножения в таких интеграторах очень проста. Она состоит из трех коныонкторов, дизыонктора и инвертора. В связи с этим схема цифрового интегратора с одноразрядными приращениями также проста.

Однако полоса пропускания таких интеграторов не превыпгает единиц герц. Для повышения их быстродействия применяют многоразрядные приращения. Но при этом схема у. 1ножения существенно усложняется и нревра цается, пo существу, в множительное устройство многоразрядных кодов.

Целью изобретения является I.oâûøñíèc быстродействия интсграторов без усложнения схемы умножения.

В предлагаемом цифровом интеграторе эта цель достигается путем использования выходного устройства, имеющего выход одноразрядIIblx и выход многоразрядных приращешш, укорочения регистра остатков на один разряд и введения схемы «ИЛ!1», дополнительного сдвига10щего регистра остатков и lpcx. уиравляемых пз устройства управления схем

«И». Схемы «Ii» включены так, что выход второго сумматора через перву1о схему «И» связан с первы.,r входо..1 схемы «ИЛИ» и че10 рез в-.орую схему «И» — co входом дополните 7brloI 0 регlIcTpri ост 1ткoв, Вьг ход I

1; со входом регистра остатков.

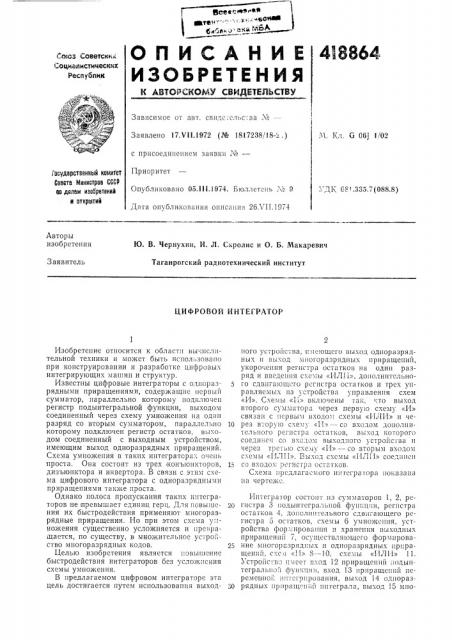

Схема предлагаемого ннтсгра гора показана на чертеже.

Интегратор состо1гг из сумматороь 1, 2, ðå20 гистра 3 нодынтсгра iblloil фуш;цни, регистра

ОетатКОВ 4, 30!lO.rlII!I ЕЛЬН0Г0 СдВ11 а10щЕГ0 рсгистра 5 остатков, схемы 6 умно>кения, устройства формирования и хранения выходных приращений 7, осуществляющего формнрова25 ние многоразрядных и одноразрядных @р.-1ращений, схс.м «11» 8 — 10, схемы <.ИЛИ» 11.

Устройство имеет ьход 12 приращений подынтегральнo i фун"!!è!i, вход 13 i!pl!pa!Il,err»i псремеппо1 . и1ггегрнрования, выход 14 однораз0 рядных нриращеш и интеграла, выход 15 мно418864

Редактор Л. Утехина

Корректор А, Степанова

Заказ 1809/10 Изд. № 591 Тираж 624 Подписное

ЫНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

"1, 1

Составитель В. Баранова

Техред Т. Курилко