Патент ссср 418982

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ 4I8982

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскин

Социалистических

Республик

Зависимое от авт. свидетельства №вЂ”

M. Кл. Н 03k 23/02

Заявлено 14. I V.1972 (№ 1772567/26-9) с присоединением заявки №

1 Приоритет

Опубликовано 05.1111974. Бюллетень Aе 9

Дата опубликования описания 25Л 11.1974

Государственный комитет

Совета Министров СССР оо делом изобретений и аткро>тнй

УДК 681.3,055:621.374..32 (088.8) Автор изобретения

В. А. Грехнев

Заявитель

ДВОИЧНЫЙ СЧЕТЧИК

Изобретение о1носится к вычислительной технике. Счетчик может быть использован в вычислительных машинах, а также в устройствах для обработки информации, работающих в реальном масштабе времени.

Известен двоичный счетчик, каждый разряд которого содержит триггер памяти и коммутационный триггер, выполненные на двух перекрестно связанных элементах «И — НЕ», и схему «И — НЕ», причем единичный выход триггера памяти соединен со входом установки в единицу коммутапионного триггера, единичный выход которого соединен со входом схемы «И — HE», а нулевой — со входом установки в единицу триггера памяти данного разряда; ьч i:Iîë схемы «И:. — 1-IE» все:.:. H3рядов, кроме старшего, соединен со входами установки коммутационного триггера последующего разряда, а в старшем разряде выход схемы «И — НЕ» соединен с одним входо;I дополнительной схемы «И — HE», выход которой соединен со входом схемы «И — HE» старшего разряда и со входами установки в нуль триггера памяти и коммутационного триггера старшего разряда. Второй вход дополнительной схемы «И — IE» и входы установки в нуль коммутационных триггеров соединены со входом счетчика.

Предлагаемое устройство отличается от известного тем, что, с целью уменьшения количества оборудования, нулевые выходы коммутационных триггеров соединены со входами установки в нуль триггеров памяти и коммутационных триггеров всех предыдущих разрядов

5 и со входом схемы «И — НЕ» предыдущего разряда, а выход дополнительной схемы

«И — HE» соединен со входами установки в нуль всех триггеров памяти и коммутационных триггеров счетчика.

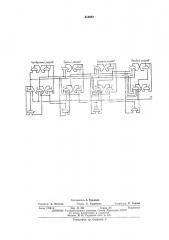

10 На чертеже изображена схема четырехразрядного двоичного счетчика.

Счетчик содержит триггеры памяти <а схемах «И — НЕ» 1 и 2, схемы «И — НЕ» 3, коммутационные триггеры на схемах «И — HE»

15 4 и 5.

В исходном состоянии все триггеры памяти находятся в нуле, на выходе схем «И вЂ” НЕ»

2 — логический нуль. Поскольку тактирующий сигнал о1сутствует, на выходах схем

20 «И — НЕ» 4, а также на выходе дополнительной схемы «И — HE» 6 — логическая единица.

Следовательно, на выходах схем «И вЂ” НЕ»

5 — логическая единица, а на выходах схем

«И — НЕ» 3 — логический нуль, Таким обраQ5 зом, с приходом первого тактирующего сигнала срабатывает только схема «И вЂ” HE» 4 первого разряда, устанавливая триггер памяти в единицу. После действия тактирующего сигнала на выходе схемы «И — HE» 3 первого

30 разряда появляется логическая единица. С

418982 приходом следующего тактирующего сигнала срабатывает схема «И вЂ” НЕ» 4 второго разряда, устанавливая триггер памяти этого разряда в единицу, а триггер памяти младшего разряда — в нуль.

Для того чтобы схема «И вЂ” -IE» 4 первого разряда не срабатывала в момент действия этого тактирующего сигнала после того как триггер памяти установится в нуль, а закже для обеспечения устойчивой работы схемы

«И — НЕ» 4 второго разряда, выход этой схемы «И — НЕ» соединен со входами третьей и четвертой схем «И вЂ” HE» первого разряда. Таким образом сигнал на выходе третьей схемы

«И — НЕ» может измениться лишь после окончания действия тактирующего сигнала. С приходом третьего тактирующего сигнала срабатывает только схема «И вЂ” НЕ» 4 первого раз- ряда, поскольку на выходах всех схем

«И — НЕ» 3 — логические нули.

По окончании действия тактирующего сигпала на выходе схемы «И — HE» 3 первого разряда появляется логическая единица, а поскольку и триггер памяти второго разряда находится в состоянии «единица», то на выходе схемы «И — НЕ» 3 второго разряда также оказывается логическая единица. Очевидно, что схемы «И — НЕ» 3 и 5 работают как полусумматор, складывая единицы переноса на разряд с состоянием триггера памяти разряда.

Таким образом, с приходом четвертого тактирующего импульса срабатывает схема

«И — НЕ» 4 третьего разряда, устанавливал триггер памяти этого разряда в единицу, а триггеры памяти младших разрядов — в нуль.

Наличие связи с выхода четвертой схемы

«И — НЕ» третьего разряда на входы схем

«И — НЕ» 4 младших разрядов, а также на вход схемы «И — НЕ» 3 предыдущего младшего разряда, опять препятствует неправильной работе счетчика. Аналогично схема «И вЂ” НЕ»

4 четвертого разряда срабатывает лишь тогда, когда триггер памяти этого разряда находится в нуле и на выходе схемы «И — НЕ» 3 третьего разряда логическая единица (это значит, что триггеры памяти предыдущих младших разрядов находятся в единице). Логическая единица на выходе схемы «И — HE» 3 четвертого разряда указывает на то, что все

5 триггеры памяти счетика находятся в единице. В этом случае срабатывает схема «И вЂ” НЕ»

6, устанавливая двоичный счетчик в исходное состояние. Наличие связей на схемы «И — НЕ»

3 и «И†HE» 4 опять препятствует неправиль10 ной работе счетчика.

Предмет изобретения

Двоичный счетчик, каждый разряд которого

15 содержит триггер памяти и коммутационный триггер, выполненные на двух перекрестно связанных элементах «И — -H Е», н схему

«И — НЕ», причем единичный выход триггера памяти соединен со входом установки в еди20 ницу коммутационного триггера, единичный выход которого соединен со входом схемы

«И — НЕ», а нулевой — со входом установки в единицу триггера памяти данного разряда; выход схемы «И — HE» всех разрядов, кроме

25 старшего, соединен со входами установки коммутационного триггера последующего разряда, а в старшем разряде выход схемы «И — HE» соединен с одним входом дополнительной схемы «И — НЕ», выход которой соединен со вхо30 дом схемы «И — НЕ» старшего разряда и со входами установки в нуль триггера памяти и коммутационного триггера старшего разряда, второй вход дополнительной схемы «И — HE» и входы установки в нуль ко vINióòàûèoííûõ

35 триггеров соединены со входом счетчика, о тл и ч а ю шийся тем, что, с целью уменьшения количества оборудования, нулевые выходы коммутационных триггеров соединены со входами установки в нуль триггеров памяти

40 и коммутационных триггеров всех предыдущих разрядов и со входом схемы «И — НЕ» предыдущего разряда, а выход дополнительной схемы «И — НЕ» соединен со входами установки в нуль всех триггеров памяти и ком45 мутационных триггеров счетчика.

418982

Пгр1ый paspsl

Отар ои paapsd"

Чгтаартый passu

7рети и разряд

Заказ 1766/18 Изд. № 599 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2

Составитель А. Кузнецов

Редактор Б. Федотов Техред 3. Тараненко Корректор О Тюрина