Устройство для управления шаговым двигателямифонд зноертоз

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 4I9850

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социал истимеских

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 03.04.72 (21) 1767323/18-24 с присоединением заявки (32) Приоритет

Опубликовано 15.03.74. Бюллетень № 10

Дата опубликования описания 08.08.74 (51) М. Кл. G 05Ь 19/40

Гасударстввииый комитет

Совета Министров СССР

Ао делам иэооретеиий и открытий (53) УДК 621,9-503.55 (088.8) (72) Авторы изобретения

С. В. Цой, Г. К. Рязанцев, В. В. Ким, О. Г. Кремер и Н. И. Чумак

Институт горного дела АН Казахской ССР (71) Заяв||гель

ФИЦ 3:Е.".-Гй (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ

ДВИ ГАТ ЕЛЯМИ

Изобретение относится к области автома1ики и вычислительной техники и предназначено для использования в системах программного управления.

Известные устройства для управления поаговыми двигателями, содержащие регистр номера двигателя, выходы которого сое.цшены через дешифратор с одними входами схем

«И», другие входы которых подклю ены к шине питания, а выходы — к первой группе выходов устройства, схему сравнения, входы которой соединены с выходами регистров заданного и текущего адресов, дешифратор состояния младших разрядов регистра теку|пего адреса, выходы которого подключены через усилители к фазовым шинам, соединенным через последовательно включенные резисторы и диоды с другой группой выходов устройства осуществляют лишь однонаправленное упра— ление, что ограничивает область их применения.

Отличием описываемого устройства является то, что оно содержит соединенные последовательно схему анализа адресов, входы которой подключены к выходам регистров заданного и текущего адресов, и блок управления, выход которого соединен с управляющим входом регистра текущего адреса.

Это позволяет расширить область применения устройства.

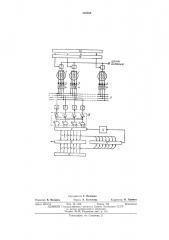

На чертеже показана функциональная схема устройства.

Здесь 1 — обмотки IlIBIoBblx двигателей;

2 — ключи; 3 — диоды; 4 — резисторы; 5— фазовые шины; 6 — усилители; 7 — схемы

«ИЛИ»; 8 — схемы «И»; 9 — регистр текущего адреса; 10 — схемы сравнения; 11 — регистр заданного адреса; 12 — схе»а анализа адресов; 13 — регистр номера двигателя с де10 шифратором 14; 15 — блок управления регистром текущего адреса 9; схемы «И» 8 и

«ИЛИ» 7 образуют дешифратор состояния 16 младших разря |ов регистра 9.

Все одноименные фазы двигателей подклю15 чены к одной шине, фазы 1 — 1 каждого двигателя расположены слева направо. Диоды 3 предусмотрены для развязки двигателей при коммутации обмоток 1 одного из них, сопротивления 4 — для форсировки скорости нар 20 стания тока в обмотках шаговых двигателей при их переключении.

Нагрузкой каждого усилителя является установившийся ток фазы двигателя.

Устройство работает следующим образом.

25 Усилители управляются от схем «ИЛИ» 7, подключенных к схемам «И» 8. Схемы «Vi», «ИЛИ» осуществляют переход от двоичного кода младших разрядов регистра 9 текущего адреса к системе напряжений, управляющих

30 включением усилителей. При работе четырехTaI:TíüIê комму l атороь IIQ схеме 1 — 2 — 3--4 сос-ояиие «OG» двух младших разрядов фнкспрустся схсмои :И» 8 и определяет включение усили,еля фазы 1; состояние «01» включает усилитель фазы II; состояние «10» включает усилитель фазы III; состояние «11» включает усилитель фазы 1, .

Так как регистр 9 текущего адреса работает в режиме счетчика, то через каждые четыре такта состоя ие егo:, ладших разр: дов судет

ПОВТорЯТЬСЯ.

Для четырехтяктпой коммутации по схе ле !

2--23 — 34 — 41 в целях перехода от кода младших разрядов регистра 9 текущего «дреса состояние «00» фиксируется схемой «И> 8 и подяетсл на схемы «ИЛИ» 7 второй ступени дешифрации элементов, которые подкл очепы и усили-елям 6 мощности фаз I и II; состояние «01» фиксируется схемой «И» 8, выход которой сое.-:,и гю схемам «ИЛИ»

7, которые сседингпотся с усилителями 6 мощности фаз 1I и I I I и т. д.

Схема 12 анализа адресов aIIa",èçI:ðóñò соде!.-жимое регистра 9 и 11 текущего и заданного адрсссв. Если содержимое регистра 11 больше содержимого регистра 9, тс регистр 9

paGoTacò как C:е чик, llа сложение. В этом случае подклю ш:отся фазы двигателя в направлении 1, 2, 3, 4 {направление двигателя прямое) . Если и:е содержимое регистра 9 больше содержимого регистра 11 заданного адреса, то схема 1 2 подаст па Олок 1 5 у11oa3 лепия регистром 9 текущего адреса сигнал, по

IIoTopo1!у б !0K 1 5 IIohlh )TéII OTcFi -. аким 00разом, что регис р текущего адреса работает как счет.I".ê, па вычитание. В этом случае фазы двигателя подключаются в направлении 4, 3, 2, 1 (Ilail! aвлепие двигателя обратное).

Гегистр 9 текуп;его адреса имеет число двоичных разрядов, доста;очное для отработки требуемого числа шагоB. В исходном состо.lнии перед каждым 1,0вым цикло .1 движепи"шагового двигателя в него заноснтс . число, равное адресу, в которсм остался этот двига5

40 тель в предыдущем цикле поиска. Это число хранится в памяти вычислительной машины.

В регистр 11 заданного адреса перед кяжды.,: новым циклом заносится код того адреса, в который должен выйти выбранный шаговый двигатель. Число разрядов его равно числу раз;.:.Дов регистра 9 влекущего адреса.

Cxe;I;I сравнения 10 осущес-являет сравнение кодов регистра 9;екущего адреса и регистра 11 заданного адреса, При равенстве кодсв схема сравпе«ия дает запрет Ila поступление сигналов в обмотки шаговых дзига-:елей.

В регистр 13 номера двигателя перед каждым новым циклом заносиIcB код номера того щагово двигателя, ко,орый должен работать в дгпшом цикле.

Предмет изобретения

Устройство для управления шаговыми двигателями, содержащее регистр номера двигателя, выходы:. торого соединены через дсшифратор с одними входами схем «И», другие входы которых подключены и шине питания, а выходы — к первой группе выходов устройства, схему сравнения, входы которой соединены с выходами регистров заданного и текущего адресов, дешифратор состояния младших разр",äîâ регистра текуьцего адресы, выходы которого подключены через усилители к фазовым шинам, соединенным через последовательно вкл оченные резисторы и диоды с другой группой выходов устройства, отл ичающееся 1ем, что, с целью расширения области применения устройства, О Io содержит соединенные последова (ельно схему анализа адресов, входы которой подключены к выходам регистров заданного и влекущего адресов, и блок управления, выход которого соединен с упрявля.ощим входом регистра текущего адреса.

419850

Составитель Е. Иванеева

Текред А. Васильева

h,oððåêToð Н. Торкнна

Редактор Б. Нанкина

Типография, по. Сапунова, 2

Заказ 1913/14 Изд. ¹ 1392 Тираж 760 Подписное

ЦИИИПИ Государственного комитета Совета Министров СССР

-o делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4 5