Распределитель импульсов

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ нц 423ll5

Союз Советскил

Социалистических

Ресвиолик

ФЯ у (61) Зависимое от авт. свидетельства (22) Заявлено 08.09.72 (21) 1826166/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 05.04.74. Бюллетень ¹ 13

Дата опубликования описания 04.09.74 (51) М. Кл. 6 06 1/04

Н 03k 17/00

1 ааударатвенный камитет

Савета Ииниатрав ССьр па делам изабретений и аткрытий (53) УДК 621.382(088.8) (72) Авторы изобретения

H. М. Бондаренко, В. И. Пустоваров, В. И. Сапрыкин и А. И. Флеров

Киевский ордена Ленина политехнический институт имени 50-летия

Великой Октябрьской социалистической революции (71) Заявитель (54) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к вычислительной и измерительной технике. Устройство может быть применено в аналого-цифровом преобразователе поразрядного кодирования.

Известны распределители импульсов, содержащие триггерный регистр, ко входам которого подключены выходы шифратора, а к выходам — входы дешифратора.

Цель изобретения — повышение быстродействия устройства и устранение возможности наложения выходных импульсов Во времени.

С этой целью в предлагаемый распределитель импульсов введены дополнительно схемы запрета и схема запуска «И», причем выходы дешифратора подсоединены ко входам шифратора через соответствующие схемы запрета, выходы которых подсоединены к инверсным входам следующих по направлению распределения схем запрета, а инверсный вход первой схемы запрета подключен к выходу схемы запуска «И», один из входов которой подключен к первому выходу дешифратора, а другой— ко входу запуска.

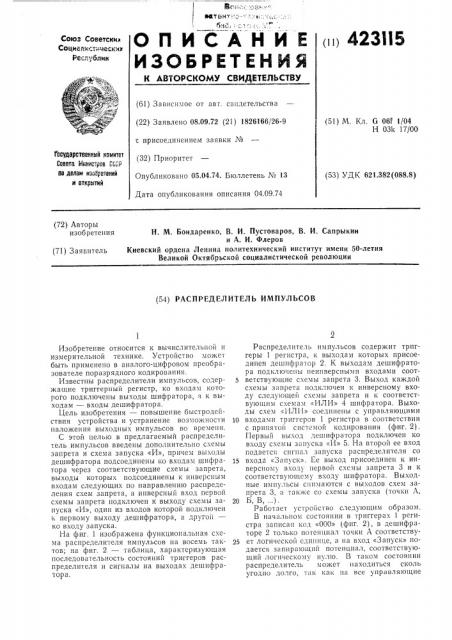

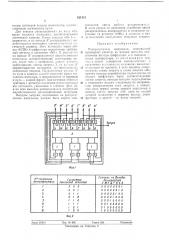

На фиг. 1 изображена функциональная схема распределителя импульсов на восемь тактов; на фиг. 2 — таблица, характеризующая последовательность состояний триггеров распределителя и сигналы на выходах дешифратора, Распределитель импульсов содержит триггеры 1 регистра, к выходам KoTOpblx присоединен дешифратор 2. К выходам дешифратора подключены неинверснымн входами соответствующие с. емы запрета 3. Выход каждой схемы запрета подключен к инверсному входу следующей схемы запрета и к соответствующим схемам «ИЛИ» 4 шифратора, Выходы схем «ИЛИ» соединены с управляющими

10 входами триггеров 1 регистра в соответствии с принятой системой кодирования (фиг. 2).

Первый выход дешифратора подключен ко входу схемы запуска «И» 5. На второй ее вход подается сигнал запуска распределителя со

15 входа «Запуск». Ее выход присоединен к инверсному входу первой схемы запрета 3 и к соответствующему входу шифратора. Выходные импульсы снимаются с выходов схем запрета 3, а такжe co cxesrbi 3anyc

Работает устройство следующим образом.

В начальном состоянии в триггерах 1 регистра записан код «000» (фнг. 2), в дешифраторе 2 только по1енцпал точки А соответству25 ет логической единице, а на вход «Запуск» подается запирающий потенциал, соответствующий логическому нулю. В таком состоянии распределитель может находиться сколь угодно долго, так как на все управляющие

423115 тельнссти цик.та раоо;f;i распредели.гсл. ..

В этом случае по окончании Отработки цикла распределитель возвращается в начальное состояние (в регистре «000»} и сстается в нем

5 до получения следую;цего импульса запуска.

Распределитель импульсов, содержа; 1ий

10 триггерпый регистр, ко входам кото;ого подкл очены выходы шифратора, а к гыходам —— гходы дешифратора, отличающийся тем, ч" 0 с целью повышения быстродействия и с i панеция «озмож11ссти пал ожени;. выходных

15 и: пульсов во времени, в него введены дополни.ельно схемы запрета и схема запуска «И», причем выходы дешифратора подсоеди ко входам шифратора через соответс-.вующие схемы запрега, выходы которых подсоединены

20 и инверсным входам следующих по награвлеf:èfo распределення схем запрета, а и11версный вход первой схемы запрета подключен к выходу схемы запуска «И», один из входов котороп подкл:очен к первому выходу деши25 фратора, а другой — — ко входу запуска, Зl Ж ЕФ Д Гу Ву Юl К луск

Заг.2

Подписное

Изд. № 696

Заказ 2150)1

Тираж 624

Типография, пр. Сапунова, 2 входы триггеров поданы потеfн1калы, cuoTB i ствующие логическому нулю.

Для запуска распределителя на вх..д «Запуск» подается потенциал, соответствующий логической единице. Схема запуска «II» 5 a— крывается, и па выходе А распредели:ел: вырабатывается потенциал,. соответс.ву:о . ий логической единице. Это Ilcтенцffàë через схемы «ИЛИ» 4 шифратора персклю1ает триггерный регистр в состояние «001». 13 результате на выходе Л распределителя вырабатывастсо потенциал, соотвстствучОьций логи !сскОму и;.л о, после чего с задержкой, равной в: смс! срабатывания схемы запрета З„ьа в,.:,:о, е и вырабатывается потенциал, со: 1ВсТс «у|ощп логической еди:п1це. Псреключен1е выхода Л из нуля в единицу ссзд"..åò передний фронт в:яходного импульса, а переключс1п.е нз единицы

В нуль — зад1!ий фронт. Лналогпчнhfь(ооразох1 триггеры 1 регистра последова" ельно гроходят все состояни",, указанные в таблице (ф11г. 2), и на всех выходах распределителя поочередно вырабатываются кратковременные импульсы.

Импульс запуска, f.одаваемый на распределитель импульсов, должен бы1ь короче .длиПредмет изобретения