Делитель частоты

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii)424146

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Респубпик (61) Зависимое от авт. свидетельства (22) Заявлено 18.07.72 (21) 1812474/18-24 (51) М. Кл. G 06f 7/44 с присоединением заявки г(е (32) Приоритет

Опубликовано 15.04.74. Бюллетень Хо 14

Государственный комитет

Совета Министров СССР оо делам изооретеиий и открытий (53) УДК 681.32(088.8) Дата опуоликовапия описания 11.09.74 (72) Авторы изобретения

Е. Н. Иванов, И. О. Пономарев и Е. Л. Якобсон (71) Заявитель (54) ДЕЛИТЕЛЪ ЧАСТОТЫ

Предлагаемое изобретение относится к области вычислительной техники, а именно к ее разделу счетно-импульсных делителей.

Известны делители, состоящие из последовательно соединенных счетных триггеров с обратными связями, определяющими коэффициент деления, например, (i — k)-ro типа тр и ггер о в.

Недостатком таких делителей является низкая помехоустойчивость, выражающаяся в том, что любая помеха, возникающая на выходе их предыдущих пересчетных схем, проходит на вход последующих и приводит к сбою всего делителя. Вероятность сбоя увеличивается при увеличении длины проводников, соединяющих вход и выход соседних пересчетных схем. Кроме того, у делителей, состоящих из последовательно соединенных синхронных пересчетных схем, счетные входы триггеров объединены в одну цепь; которая, в зависимости от коэффициента деления, может быть достаточно длинной. Любая помеха, возникшая в этой цепи, приводит к сбою делителя.

Цель предлагаемого изобретения заключается в повышении помехоустойчивости делителя частоты.

Эта цель достигается тем. что раздельные входы триггеров каждой пересчетной схемы подключены ко входу инвертора этой схемы и к выходу соответствующей схемы «И—

НЕ», один вход которой соединен с выходом предыдущей пересчетной схемы, а другой вход связан со счетными входами ее триггеров непосредственно, а с раздельными входами — через инвертор.

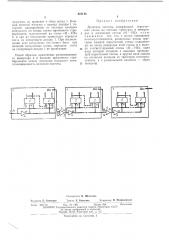

Схема одного из возможных вариантов реализации делителя приведена на чертеже.

Делитель частоты может быть составлен из

10 любого числа пересчетных схем с любым коэффициентом деления. Рассмотрим случай, когда пересчетная схема представляет собой декаду 1, состоящую из некоторого числа определенным образом соединенных, например ((— К)-го типа триггеров 2. Вход 3 каждой декады 1 подключен к объединенным (раздельным) 1 и К входам триггеров 2 непосредственно. а к счетным входам своик (1 — К)-го типа триггеров 2 — через инвертор 4. Декады 1 разделены схемой «И вЂ” НЕ» 5, входы которой связаны с выходом предыдущей декады 1 и со счетными входами К-го типа триггеров 2.

Работает делитель частоты следующим об25 pазом.

В интервале между счетными импульсами, поступающими с инверторов 4. все (1 — К)-го типа триггеры 2 закрыты по I и К входам 3 положительным сигналом, и любая помеха, ЗО не совпадающая по знаку со счетными им424146

Предмет изобретения

C3I 43

1

LЮ

Составитель И. Шелипова

Редактор Е. Семанова Техред Е. Ьорисова Корректор И. Позняковская

Заказ 2311, 15 Изд. № 1491 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 5К-З5, Раушская наб., д. 4j5

Типография, пр. Сапунова, 2 пульсами, пс приводит к сбою декад 1. Каждый десятый импульс с выхода декады 1 поступает одновременно со счетным входным импульсом па входы схемы временного стробировапия, вьшолнс ной на схеме «И вЂ” НЕ»

5, и при пх совпадении происходит передача света па следующую декаду 1. При несовпадении этих импульсов, что может быть при наличии импульсных помех, передача счета на следующую декаду 1 не происходит.

Таким образом, применение развязывающего инвертора 4 и наличие временного стробирования между декадами повышает помехозащищенность делителя частоты.

Делитель частоты, содержащий пересчетные схемы на счетных триггерах и инверторах и логические схемы «И — НЕ», отлич а ющи йся тем, что, с целью повышения помехоустойчивости, раздельныс входы триггеров каждой пересчетной схемы подключены ко входу инвертора этой схемы и к выхото ду соответствующей схемы «И — НЕ», один вход которой соединен с выходом предыдущей пересчетной схемы, а другой вход связан со счетными входами ее триггеров непосредственно, а с раздельными входами — через

15 инвертор.