Патент ссср 425176

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пп 425I76

Союз Советских

Социалистических

Республик (61) Зависимое от авт, свидетельства (22) 3 аявлено 02.06.72 (21) 1791612/18-24 с присоединением заявки № (32) Приоритет (51) Л1, Кл. О 061 7/50

Государственный комитет, Совета Министров СССР во денаи изооретвний и открытий

Опубликовано 25,04.74. Бюллетень Ы 15 ! Дата опубликования описания 01.10.74 (53) VQIi 681.325.54 (088,8) (72) Авторы изобретения

С. О. Мкртчян и H. Ш. Вартанян (71) Заявитель (54) КОМБИНАЦИОННЪ|Й СУММАТОР-ВЫЧИТАТЕЛЪ

Изобретение относится к области автоматики и вычислительной техники.

Известен комбинационный сумматор на пороговых элемента,;, включающий цепи суммирования и переноса. Известное устройство сложно Ilo конструкции, особенно при реализации сумматора-вычитателя, так как содержит большое количество логических элементов, а управление режимами сложения и вычитания осуществляется двумя раздельными шинам и.

Целью изобретения является упрощение устройства.

Это достигается тем, что управляющий вход устройства соединен в каждом разряде с первыми входами первого формального нейрона (ФН) и первого элемента ИЛИ, входы первого числа соединены в каждом разряде со вторыми входами первого ФН и первого элемента ИЛИ и с первыми входами второго ФН и второго элемента ИЛИ. Выход первого элемента ИЛИ соединен с третьим входом первого ФН, выход которого соединен с первым входом мажоритарного элемента (МЭ). Входы второго числа соединены в каждом разряде со вторым входом МЭ и с первыми входами третьего ФН и третьего элемента ИЛИ.

Выход третьего ФН соединен со вторыми входами второго ФН и второго элемента

ИЛИ, выход которого соединен с третьим входом второго ФН. Выходы второго ФН в каждом разряде соединены с выходами устройства. Выход МЭ каждого соседнего младшего разряда соединен с третьим входом МЭ и со вторыми входами третьего ФН и третьего элемента ИЛИ каждого соседнего старшего разряда. Входы третьего элемента ИЛИ соединены с третьим входом третьего ФН. Третий вход МЭ младшего разряда соединен со вхо10 дом устройства. Выход МЭ старшего разряда соединен с выходом устройства.

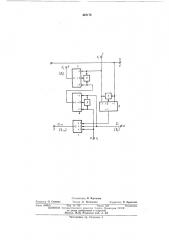

I13 чертеже показан один разряд комбинационного сумматора-вычитателя.

В каждом разряде устройства содержится

15 одllll трехвходовый ЧЭ 1. входы которого имеют вес +1, а порог равен +2, и три идентичных ФН 2, 3 и 4 с входными элементами

ИЛИ 5. Два входа ФН имеют вес — 1, третий вход имеет вес +2, а порог равен +1. Выход

20 элемснта ИЛИ в каждом ФI I подключен ко входу с весом +2. Управляющий вход 6 устройства соединен в каждом разряде с первымп входами первого ФН 2 и первого элемента ИЛИ. Входы Х; первого числа 7 соединены

25 в каждом разряде со вторыми входами первого ФН 2 и первого элемента ИЛИ, и с первыми входами второго ФН 3 и второго элемента

ИЛИ. Выход первого ФН 2 соединен с первым в.;.одо;i,ЧЭ l. Входы ц; второго числа 8

30 соединены в каждом разряде со вторым вхо425176

3 дом МЭ 1 и с первыми входами третьего ФН 4 и третьего элемента ИЛИ. Выход третьего

ФН4 соединен со вторыми входами второго

ФН 3 и второго элемента ИЛИ. Выходы второго ФН 3 в каждом разряде соединены с выходами 9 устройства. Выход МЭ 1 ка?кдого соседнего младшего разряда соединен с третьим входом МЭ 1 и со вторыми входами третьего ФН 4, и третьего элемента ИЛИ каждого соседнего старшего разряда. Третий вход

МЭ 1 младшего разряда соединен со входом

10 устройства, а выход МЭ старшего разряда соединен с выходом 11 устройства.

Комбинационный сумматор-вычитатель работает следующим образом.

Если на управляющей шине 6 имеется низкий потенциал (U=O), rî устройство работает в режиме сложения, 5=Х+ Y. Обозначим су.мму в L-ом разряде через S;, а перенос в старший разряд — через С;ч1.

1 ыссмотрим работу двухразрядного устройcãâ2 при U=O.

Допустим, С;=-О. Нри подаче на входы схемы шсел х=1 (следовательно, х! 1, х=

== О) и У=2 (следовательно, gi — — О, д.-= 1) в первом разряде возоу?кдаются первьш 2 и второй 3 ФН, а МЭ 1 не Возбуждается. СледоВательно, в 1ервом разряде имеем Si 1, C? О. Во в!ором разряде возбуждаются второй 3 и третий 4 ФН, а МЭ 1 не возбуждается. Следовательно, здесь имеем 5 =1, С =О.

Таким образом, в су".ямаrope получим 5,=1, S2=- >, т. е. S=õ+Y — 3.

Допустим, что Х=З (Х,=-1, Лq- 1), У=1 (g;=1, g:=0). Б первом разряде возбу?кдаются первьш 2 и третий 4 ФН и МЭ 1, а втор 011 Ф1 1 3 нс Возоужд2с! С!1, так 1(ак на Обоих его входах пме1отся высокие потенциалы. Следовательно, 5! =О, C = 1. Во втором разряде также возбуждены первьш 2 и третий 4 ФН и

МЭ 1, а второй ФН 3 не возбужден. Следовательно, 5>=-0, C>= — 1. Таким образом, в сумматоре получим 5=Х+У=4.

Суммирование чисел при других значениях

Х и У осуществляется "íà,ë"îãè÷íûì ооразом.

Если на шине б имеется высокий потенциал (Ь =1), то устройство работает в режиме вычитания, D = Х вЂ” У. Обозначим разность в

I-o11 разряде через D;> а затем пз старшего разряда — через Л! В1.

Рассмотрим работу усгро11ства при U= 1.

Пусть Х=З (х,=-1, х =1), Y=2 (у!=0, «!1>=1), тогда в первом разряде возбуждается только второй ФН 3. Следовательно, D, = 1, Z..==-- О. .Во втором разряде возбужден только

Т1зег11!! ФН 4. Следовательно, 0 =О, Z> — — О.

Таким Ооразом, на Выходах устроиств2 пол у ч 2 е м О1 = 1, D. = =O, т, е. D = X — Y = 1. . (Опустим, Х=-2 (х,=0, х> — — 1) и У=1

igI —— 1> !> =0), тогда в первом разряде возбуждаются все элементы. Следовательно, 5

15

Di=1, 1 =1. Во втором разряде возбуждается только трег1ш ФН 4, следовательно, Dq — — О, Zs — — О. В результате на выходе устройства получаем D=X — У=1.

Вычитание чисел при других значениях Х и

У осуществляется аналогичным образом.

Таким образом, при U=O устройство работает как двоичный комбинационный сумматор, а при U=1 как двоичный комбинационный вычитатель.

Время пробега переноса — займа в и-разрядном комоинационном сумматоре — вычитатсле равно проб (и 1) > где т — задер?кка мажоритарного элемента.

Предмет изобретения

Комбинационный сумматор — вычитатель, содержащий в ка?кдом разряд: один трехвходовьш ма?коритар ы элемент, каждый вход которого имеет вес +1, а порог равен +2, и три формальных нейрона, соединенные с соОтвстству 1О1цп>1и элемеп гам!1 И.1И, д22 Входа формального нейрона имеют вес — 1, третий вход имеет вес +2, а порог равен +1, о тл ич а ю шийся тем, что, с целью упрощения устройства, управля1ощий вход устройства соединен в каждом разряде с первыми входами первого формального нейрона и первого элемента ИЛИ, входы первого числа соединены

В к2и(дом разряде со Вторыми Входами первого формального нейрона и первого элемента

ИЛИ и с первыми входами второго формального нейрона и второго элемента ИЛИ, выход первого элемента ИЛИ соединен с третьим входом первого формального нейрона, выход которого соединен с первым входом M2?KopHтарного элемента, входы второго числа соединены в каждом разряде со вторым входом мажоритарного элемента и с первыми входами третьего формального нейрона и третьего элемента ИЛИ, выход 1ретьего формального нейрона соединен со вторыми входами второго формального нейрона и второго элемента

ИЛИ, выход которого соединен с третьим входом второго формально!о нейрона, выходы второго формального нейрона в каждом разряде соединены с выходами устройства, выход мажоритарного элементы каждого соседнего младшего разряда соединен с третьим входом ма?коритарного элемента и со вторыми входами третьего формального нейрона и третьего элемента ИЛИ каждого соседнего старшего разряда, выходы 1ретьего элемента ИЛИ соединены с третьим входом третьего формального нейрона, тре-ий вход мажоритарного элемента младшего разряда соединен со входом устройства, выход мажори>арного элемента старшего разряда соединен с выходом устройства.

425176

Составитель Н. Вартанян

Техред Л. Богданова

Редактор О. Стенина

Корректор В. Бры ксина

Типография, пр, Сапунова, 2

Заказ 2688/2 Изд. М 765 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, K-35, Раушская наб., д. 4/5