Запоминающее устройство аппаратуры передачи данных с автоматическим запросол! ошибок

Иллюстрации

Показать всеРеферат

1 енкт, .

1 (.

«>425369

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидстельства— (22) Заявлено 23.12.7) (21) 1728153 26-9. с присоединением заявки ¹â€” (32) Приоритет—

Опубликовано 25.04.74. Бюллетень ¹ 15

Дата опубликования описания 15.! 1.74 (51) Ч. Кл. Н 04125 00

Государственный ивмнтет

Совета Министров СССР пв делам изобретений н открытий (53) УДК 621.394.395 (08М) (72) Авторы

:изобретен.ия (71) Заявитель

Л. К. Дуничева, К. Е. Макаров и Ю. Д. Халезов (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО АППАРАТУРЫ

ПЕРЕДАЧИ ДАННЫХ С АВТОМАТИЧЕСКИМ

ЗАПРОСОМ ОШИБОК

Изобретение относится к области телеграфной связи, а именно к запоминающим устройствам аппаратуры передачи данных с автоматическим запросом ошибок.

Известно запоминающее устройство, содержащее накопитель координатного тила с двумя формирователями управляющих сигналов, выходы координат которого соответственНо соединены с последовательно соединенными сборками, дешифраторами и счетчиками.

Цель изобретения — уменьшение количества требуемых адресов.

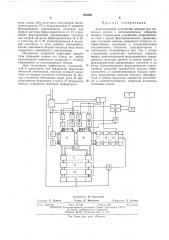

Для этого в предлагаемое запоминающее устройство введен дополнительный формирователь управляющих сигналов, причем ко входу одного из формирователей управляющих сигналов и ко входу дополнительного формирователя управляющих сигналов подключены выходы .переключателя, к соответствующим входам которого, подключены выходы каждого дешнфратора, а между выходами координат накопителя и соответствующими сборками включены ключевые схемы, На чертеже приведена функциональная схема запоминающего устройства.

Выходы распределителя 1 подключены к формирователям 2 и 8 управляющих сигналов по ос» У, к схемам «И» 4 — 7 и ко входу переключателя 8. Выходы переключателя 8 подключены ко второму входу схем «И» 4 — 7.

Третий вход схем «И» 5 и 7 связан с источником 9 кодовых комбинаций через схему 10 ввода; Выходы схем «И» 4 — 7 соединены с формировяTåë51ми 11 — 14 управляющих сигналов по осп Х. Формирователи 2 и 3 подключены к горизонтальным (ocb 1 ) шинам зяпнсн и чтения матриц 15 и 16, соединенным последовательно (на чертеже условно показаны первая,,вторая и последняя группа шин) с накопителем координатного тп па. Выходы шнн соединены со сборками «ИЛИ» 17 ня два входа каждая, выходы которых поступают на ключевые схемы «И» 18.

На второй вход ключевой схемы «И» поступают сигналы с дешифратора 19 состояний счетчика 20. Выходы вертикальных шин матриц 15 и 16 соединены со сборками «И,ЧИ» 21 ня четыре входя, выхо lbl которых подключены к кл.очевым схемам «И» 22, па второй вход ключевых схем «И» поступают сигналы с дешпфратора 28 состояний счетчика 24. Обмотка считывания мятриц подключена к усилителю считывания 25, выход которого соединен с блоком 26 преобразования. Выход блока преобразования подключен к блоку 27 вторичного вывода. Счетчики 24 и 20 соединены последовательно через схему «И» 28.

Тактовые импульсы высокой частоты и низкой частоты поступают на распределитель

1, на выходе которого формируются нмпуль425369

55

65 сные последовательности Tl, T2, Т3, сдвинутые друг относительно друга на семь лксек.

Тактовые импульсы низкой частоты, кроме того, поступают на четырехразрядный счетчик

24 адресов. ,Весь объем накопителя координатного типа разделен на две матрицы (5 и 16 для упрощения схемы,и уменьшения количества активных элементов. По оси Y шины чтения и записи матриц соединены последовательно. На вход формирователя 2 поступает импульсная последовательность Т! с выхода распределителя l. Сформированный управляющий сигнал с выхода формирователя 2 поступает параллельно на все шины чтения по оси Y.

На вход формирователя 8 поступает импульсная последовательность Т2 с выхода распределителя l. Сформированный управляющий сигнал с выхода формирователя 8 поступает параллельно на все шины записи по оси Y.

Для формирования управляющего сигнала

«Чтение Х!» для первой матрицы импульсная

:последовательность Tl поступает на вход схемы «И» 4, на,другой вход которой поступает сигнал «Разрешение» из переключателя 8.

С выхода схемы «И» 4 сигнал поступает на вход формирователя 11 управляющего сигнала «Чтение Х!». С выхода формирователя сигнал поступает параллельно на все шины чтения первой матрицы.

Для формирования управляющего сигнала

«Чтение Х2» для второй матрицы импульсная последовательность Т! поступает на вход схемы «И» 6, на другой вход которой поступает сигнал «Разрешение» из переключателя 8. С выхода схемы «И» 6 сигнал поступает на вход формирователя И управляющего сигнала

«Чтение Х2».

С выхода формирователя сигнал поступает на все шины чтения второй матрицы.

Для формирования сигнала «Запись Хl» для первой матрицы импульсная последовательность Т2 с выхода распределителя поступает на вход схемы «И» 5. На второй вход схемы «И» 5 поступает сигнал «Разрешение» из переключателя 8. На третий вход схемы

«И» 5 поступает сигнал «Информация» из источника 9 кодовых комбинаций через схему

10 ввода информации. С выхода схемы «И» 5 сигнал поступает на вход формирователя 12, с выхода которого сформированный сигнал

«Запись Х!» поступает параллельно на все шины записи первой матрицы 15.

Для формирования сигнала «Запись Х2» для второй матрицы импульсная последовательность Т2 с выхода распределителя 1 поступает на вход схемы «И» 7. На второй вход схемы «И» поступает сигнал «Разрешение» цз переключателя 8. На третий вход схемы «И»

7.поступает сигнал «Информация» из лсточнпка 9 кодовых комбинаций через схему 10 ввода инфсрмации. С выхода схемы «И» 7 сигнал поступает па вход формирователя 14, с вы. ода которого сформированный сигнал «Запись

Х2» поступает параллельно на все шины записи второй матрицы (б.

Такое построение устройств формирования управляющих сигналов позволяет отказаться от использования обмоток компенсации в матрицах, что значительно улучшает помехоустойчивость ii снижает требования к схеме усилителя воспроизведения, а также, позволяет значительно упростить усгройство адресации.

Для формирования адресов Х первой и второй матриц тактовые импульсы низкой ча. стоты поступают на вход счетчика 24. Выходы разрядов счетчика 24 поступают в дешифратор 28. Сигналы с выходов дешифраторов 28 поступают на ключевые .схемы «И> 22. Количество разрядов счетчика, схем «И» в дешифраторе и ключевых схем определяется количеством столоцов Х одной матрицы.

Шины «Запись» и «Чтение» Х! первого столбца матрицы 15 соединены со сборкой

«ИЛИ» 21, на четыре входа для каждого столбца Х. На другие два входа поступают шины «Запись» и «Чтение» Х2 первого столоца матрицы 16. Ооъединенный сигнал с выхода сборки «ИЛИ» 21 поступает на ключевые схемы «И» 22. При наличии сигнала с дешифратора 28 ключевая схема открывается и создается цепь для прохождения сигналов

«Записи и Чтения» по столбцу Х в первую или вторую матрицу в,зависимости от того, работают формирователи ll и 12 или (8 и 14.

Аналогичным образом формируются адреса на оси У. Счетчик 20 адресов У соединен последовательно со счетчиком Х через схему

«И» 28. На один вход схемы «И» 28 поступает последнее состояние счетчика 24 с дешифратора 28. На другой вход — тактовые импульсы низкой частоты. Таким образом после заполнения счетчика 24 (т. е. отработки всех столбцов Х) идет сигнал на переключение счетчика У. Выходы разрядов счетчика 20 поступают в дешифратор 19 счетчика. Сигналы с выходов дешифратора 19 поступают на ключевые схемы «И» 18. Количество разрядов счегчика, схем «И» ta дешифраторе и ключевых схем определяются количеством строк Y в матрице. Шины «Запись» и «Чтение» Y матрицы 16 соединены со сборкой «ИЛИ» 17 на два входа для каждой из строк Y. Объединенный сигнал с вывода сборки «ИЛИ» 17 .поступает на ключевую схему «И» 18. При наличии сигнала с дешифратора 19 ключевая схема открывается и создается цепь для прохождения сигналов «Чтения и Записи» по строке Y.

Из всего количества сердечников только для одного произойдет суммирование управляющих сигналов. С приходом следующего такта низкой частоты счетчик переключится и будет работать следующий сердечник. После того, как полностью отработает первая матрица 15, т. е. досчитают до заполнения счетчики 24 .и 20 на схему «И», расположенную в переключателе 8, поступают сигналы переполнения счетчиков 24 и 20, на третий

425369

Предмет изобретения

Составитель Н. Герасимова

Техред Л. Богданова

Корректор В. Гутман

1 едактор О. Кунина

Заказ 1679/336 Изд. М 842 Тира>к 678 Поди испое

Ц11ИИПИ Государственного комитета Совета Министров СССР по делам изобретений п открытий

Москва, Ж-35, Раугискап наб., д. 4, 5

Тип. Харьк. фил. пред. «Патент». вход схемы «И» поступает импульсная последовательность Т3 и переключатель 8 запретит формирование управляющих сигналов для первой матрицы формирователям 11, 12 и разрешит формирование управляющих сигналов для второй матрицы формирователям И и 14, а счетчики 24 н 20 устанавливаются в исходное состояние и цикл работы повторяется.

После заполнения второй матрицы весь объем накопителя оказывается заполненным.

Построение устройств адресации накопителя позволяет менять его объем на любое произвольное количество разрядов в сторону уменьшения от максимального объема.

Для считывания информации, запоминаемой в накопителе, все сердечники пронизаны обмоткой считывания, .выходы которой соединены со входом усилителя считывания 2о. Выход усилителя считывания через блок 26 преобразования подключен к блоку 27 вторичного вывода устройства передачи информации.

Запом11нающее устройство аппаратуры передачи данных с автоматическим запросом ошибок, содержащее накопитель координатного типа с двумя формирователями управляющих сигналов, выходы координат которого соответственно соединены с последовательно соединенными сборками, дешифраторами If счетчиками, отличающееся тем, что, с целью уменьшения количества требуемых адресов, введен дополнительный формирователь управляющих сигналов, причем ко |входу одного из формирователей управляющих сигналов и ко

15 входу дополнительного формирователя управляющих сигналов подключены выходы переключателя, к соответствующим входам которого подключены выходы каждого дешнфратора, а между выходами координат накопите2О ля и соответствующими сборками включены ключевые схемы.