Селектор импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Совхоз Советских

Социалистических

Республик

-«i 428545 (61) Зависимое от авт. свидетельства— (22) Заявлено 20.06.72 (21) 1797530/26-9 (51) М. Кл. Н 03k 5/20 с прпсоед шепшсм заявки ¹ ——

1 осударственный комитет

Сонета й1иниотрон СССР оо делам изооретений и открытий (32) Приоритет—

Опубликовано 15.05.74. Бюллетень № 18

Дата опубликования описания 28.1.75 (53) УДК 621.374.33 (088.8) (72) Автор изобретения

Ф. К. Лежнин (71) Заявитель

3

t (54) СЕЛEKTOP ИМПУЛЬСОВ

Предлагаемое изобретение относится к области радиотехники и может быть использовано в аистемах автоматики, в частности, для выделения заданного значения частоты частотно-модулированного сигнала по величине его полупериода.

Известны селекторы импульсов, содержащпе схему совпадения, запоминающее устройство.

Недостатком известных систем является невозможность автоматического возвращения запоминающего устройства в требуемое соcronnnc прн сбое его помехами, поэтому помехоустойчивость такого селектора недостаточна.

С целью повышения помехоустойчивости в предлагаемый селектор дополнительно введена логическая схема Шеффера, выход которой соединен со вторым входом запомпнающего устройства, а входы подключены ко входам схемы совпадения.

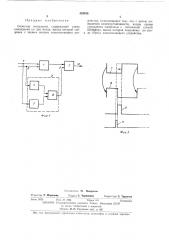

1-1а (риг. 1 приведена схема предлагаемого селектора; иа фиг. 2 — Bpe «enпыс диаграммы его работы.

Селектор состоит из схемы совпадения 1, - апомппающего устройства 2 и логической схемы Шеффера 8, включающей в себя два инвертора 4 и 5 и схему совпадения 6.

Работа селектора заключается в следующем.

До момента сравнения длительности импульса 7 с заданной длительностью импульса 8 (см. фиг. 2), передний фронт которого совпадает с передним фронтом импульса 7, с выхода схемы 8, выполняющей логическую операцию у=а.b, на:второй вход запоминающего устройства 2 поступают импульсы 9, длительность которых равна разности длительностей импульсов 7 и 8. В случае переброса

ip помехой запоминающего устройства 2 нос. леднее импульсом 9 автоматически переводится в исходное состояние «О» не более, чем через время Т (T — мгновенное значение периода импульсов 7).

После того, как длительность импульса 7 станет меньше длительности импульса 8, на выходе селектора 10 (см, фпг. 1) появляется потенциальпьш сигнал «1», так как исчезают

20 импульсы 9, но возникают выходные импульсы 11 схемы совпадения 1 на первом входе устройства 2, которыми оно выводится из исходного состояния «О».

25 Согласно фиг. 1 можно выполнить селектор длительности положительных и отрицательых импульсов с потенциальным входом как для случая увеличения, так и для случая уменьшения длительности селектируемых имзп пульсов.

428545

Предмет изобретения

Фиг, 2

Составитель М. Панкратов

Р< дактор Т. Морозова Техред 3. Тараненко 1 орректор 3. Тарасова

Заказ 5023 Изд, ¹ 1604 Тираж 811 Подписное

ЦНИИПИ Государственного коки1тета Совета М|шистров СССР ио депаги изобретений п открытий

Москва, 7К-35, Раушская наб., д. 4/5

Обл. тпп. 1(острогиского управления издательств, иолиграф|ш п книжной торговли

Селектор импульсов, содержащий схему совпадения на два входа, выход которой соединен с первым входом запоминающего устройства, отлнча ощиася тем, что, с целью повышения помехоустойчивости, входы схемы совпаденп1я соединены с логической схемой

Шеффера, выход которой подключен ко вхо5 ду сброса запоминающего устройства.