Многоустойчивый элемент с 2/v+1 устойчивымисостояниями

Иллюстрации

Показать всеРеферат

(ii) 429537

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (б1) Зависимое от авт. свидетельства (22) Заявлено 04.07.72 (21) 1804316/26-9 с присоединением заявки ¹ (32) Приоритет

Опубликовано 25.05.74. Бюллетень № 19

Дата опубликования описания 10.11.74 (51) М. Кл. H ОЗЕ 23/02

Государственный комитет

Совета Министров СССР ло делам иэооретений и открытий (53) УДК 621.374,32 (088.8) (72) Авторы изобретения

Н. A. Дзюндзик, Ю. В. Азаров и Ю. С, Крылов (71) Заявитель (54) МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ С 2N+1 УСТОЙЧИВЫМИ

СОСТОЯ Н ИЯМИ

Изобретение относится к построению узлов вычислительной техники и дискретной автоматики в микроэлектронном исполнении, в частности в виде больших интегральных схем.

Известный многоустойчивый элемент с

2V+1 устойчивыми состояниями (где N=1, 2, 3 ...) построен в логическом базисе «И—

ИЛИ вЂ” 1-1Е» на основе одного триггера памяти, имеющего 2Л +1 устойчивых состояний, и одного коммутационного триггерного устройства, синхронизирующего переключение триггера.

Цель изобретения — упрощение схемы многоустойчивого элемента и уменьшение его потребляемой мощности.

Для этого многоустойчивый элемент с

2N+1 устойчивыми состояниями (где N=1, 2, 3...) строится на основе соединения одного триггера памяти с 2Л +1 устойчивыми состояниями и одного коммутационного триггерного устройства, производящего пересчет 2N входных импульсов по модулю 2, регистрацию

2У-го импульса и сбрасываемого в исходное состояние . задним фронтом (2N+1) -ro импульса, и осуществляет пересчет входных импульсов по модулю 2N+1 в коде «1 из (2Л +1)».

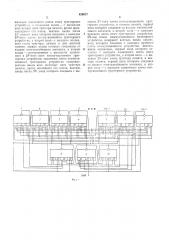

На фиг. 1 . представлена функциональная схема. предлагаемого многоустойчивого элемента с 2Л +1 устойчивы.;и состояниями; на фиг. 2 — таблица состояний этого элемента.

Многоустойчивый элемент с 2N+1 устойчивыми состояниями (где N=1, 2, 3...) построен в логическом базисе «И вЂ” ИЛИ вЂ” HE» и образован соединением триггера памяти с 2N+1

5 устойчивыми состояниями (1 — 4 ... 5 — 7) и коммутационного триггерного устройства 8—

10, производящего пересчет 2N входных импульсов по модулю 2, регистрирующего 2Nный импульс и сбрасываемого в исходное со10 стояние задним фронтом (2N+1)-го импульса.

Плечи триггера памяти содержат по одному вентилю 11 — 17 ввода информации и по одному вентилю 18 — 24 памяти для образова15 ния триггерных связей: входы вентиля памяти любого плеча триггера памяти соединены с выходами всех остальных плеч этого триггера. Информационный (счетный) вход многоустойчивого элемента с 2Л +1 устойчивыми

20 состояниями соединен с первыми входами вентилей ввода информации всех плеч триггера памяти и со входами вентилей 25 — 28 памяти коммутационного триггерного устройства. Вторые входы вентилей ввода информации всех

25 нечетных (кроме последнего) плеч триггера памяти соединены с выходом нулевого плеча 8 коммутационного триггерного устройства, а вторые входы вентилей ввода информации всех четных плеч триггера памяти — с выхо30 дом единичного плеча 9 этого триггерного устройства, 429537

15

Второй вход двухвходного вентиля ввода информации последнего плеча триггера памяти соединен с 2N-ным плечом коммутационного триггерного устройства. Остальные входы вентилей ввода информации всех нечетных (кроме последнего) плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча, в том числе последнего — для первого и предпоследнего плеча; остальные входы вентилей ввода информации всех четных плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча и последнего плеча.

Нулевое плечо 8 коммутационного триггерного устройства содержит: вентиль 29 ввода

«единицы», первый вход которого соединен с выходом единичного плеча 9 этого триггерного устройства, а остальные входы — с выходами всех четных плеч триггера памяти, кроме предпоследнего его плеча; вентиль 30 ввода числа 2N, первый вход которого соединен с выходом 2У-го плеча коммутационного триггерного устройства, а второй вход — с выходом последнего плеча триггера памяти; два вентиля 25 и 2б памяти, вторые входы которых соединены соответственно с выходами

2N-го и единичного плеч коммутационного триггерного устройства.

Единичное плечо 9 коммутационного триггерного устройства содержит: вентиль 31 ввода «нуля», первый вход которого соединен с выходом нулевого плеча 8 этого триггерного устройства, а остальные входы — с выходами всех нечетных плеч триггера памяти, кроме последнего его плеча; вентиль 32 ввода числа

2У, вход которого соединен с выходом 2N-ro плеча 10 коммутационного триггерного устройства; вентиль 27 памяти, вход которого соединен с выходом нулевого плеча 8 этого триггерного устройства.

2У-ное плечо 10 коммутационного триггерного устройства содержит: вентиль 33 ввода

«нуля», вход которого соединен с выходом нулевого плеча коммутационного триггерного устройства; вентиль 34 ввода «единицы», первый вход которого соединен с выходом единичного плеча этого триггерного устройства, а второй вход — с выходом 2¹o плеча триггера памяти, и вентиль 28 памяти, второй вход которого соединен с выходом единичного плеча коммутационного триггерного устройства.

Принцип работы многоустойчивого элемента с 20+1 устойчивыми состояниями (где

N= l, 2, 3 ...) состоит в том, что при,поступлении входных импульсов будет переключаться одно плечо триггера памяти, выбор которого определяется только состояниями предыдущего (или последнего — для первого) плеча этого триггера и коммутационного триггерного устройства. При этом импульсы с выходов нулевого и единичного плеча коммутационного триггерного устройства управляют переклю25

65 чением 2N плеч (с первого по 2N-ное включительно) триггера памяти, а импульс с выхода 2N-го плеча этого триггерного устройства управляет переключением (2М+1) -го плеча триггера памяти. После окончания входного (счетного) импульса коммутационное триггерное устройство переключится в новое состояние — в соответствии с новым состоянием триггера памяти. На фиг. 2 показаны последовательные состояния многоустойчивого элемента с 2N+1 устойчивыми состояниями (где

N=1, 2, 3 ...), определяемые выходами всех плеч триггера памяти.

Многоустойчивый элемент с 2N+1 устойчивыми состояниями (где Л =-l, 2, 3 ...) имеет быстродействие, определяемое временем переключения четырех логических схем «И вЂ”ИЛИ вЂ” НЕ» имеет минимальную величину потребляемой мощности, так как в таком элементе всегда открыты только три инвертора (схемы «И — ИЛИ вЂ” НЕ»).

Предмет изобретения

Многоустойчивый элемент с 2N+1 устойчивыми состояниями (где N=1, 2, 3 ...), построенный в логическом базисе «И вЂ” ИЛИ—

НЕ» на основе одного триггера памяти, имеющего 2N+1 устойчивых состояний, и одного коммутационного триггерного устройства, синхронизирующего переключение триггера памяти, отличающийся тем, что, с целью упрощения схемы многоустойчивого элемента и уменьшения величины потребляемой мощности, каждое плечо триггера памяти содержит по два вентиля — вентиль памяти, входы которого соединяются с выходами всех остальных плеч этого триггера, и вентиль ввода информации, причем первые входы всех этих вентилей соединены со входом многоустойчивого элемента, вторые входы вентилей всех нечетных, кроме последнего, плеч триггера памяти соединены с выходом нулевого плеча коммутационного триггерного устройства, а вторые входы вентилей ввода информации всех четных плеч триггера памяти — с выходом единичного плеча этого триггерного устройства; второй вход вентиля ввода информации последнего плеча триггера памяти соединен с выходом 2N-ного плеча коммутационного триггерного устройства; остальные входы вентилей ввода информации всех нечетных, кроме последнего, плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча, в том числе последнего — для первого; остальные входы вентилей ввода информации всех четных плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча и последнего плеча; коммутационное триггерное устройство имеет нулевое, единичное и 2N -ное плечи, причем нулевое плечо содержит: вентиль ввода

«единицы», первый вход которого соединен с

429537

Z,V+ 7

5 0

Вхоо выходом единичного плеча этого триггерного устройст, а остальные входы — с выходами всех четных плеч триггера памяти, кроме предпоследнего сго плеча; вентиль ввода числа

2Х, первый вход которого соединен с выходом

2N-ного плс а коммутационного триггерного устро ici ва, а второй вход — с выходом последнего плеча триггера памяти и два вентиля памяти, первые входы которых соединены со входом многоустойчивого элемента, а вторые входы — соответственно с выходами единичного и 2У-ного плеч коммутационного триггерного устройства; единичное плечо коммутационного триггерного устройства содержит: вентиль ввода всех нечетных плеч триггера памяти, кроме последнего его плеча; вентиль ввода числа 2N, вход которого соединен с выходом 2У-ного плеча коммутационного триггерного устройств», и гсптиль памяти, первый вход которого соединен со входом многоустойчивого элемента, а второй в. од — с выходом нулевого плеча этого триггерного устройства;

2Ж-ное плечо коммутационного триггерного устройства содержит: вентиль ввода «нуля», вход которого соединен с выходом нулевого плеча коммутационного устройства, вентиль

10 ввода «единицы», первый вход которого соединен с выходом единичного плеча этого триггерпого устройства, а второй вход — с выходом 2Л -ного плеча триггера памяти, и вентиль памяти, первый вход которого соединен

15 со входом многоустойчивого элемента, а второй вход — с выходом единичного плеча коммутационного триггерного устройства.

429537

Раг. 2

Составитель Н. Дубровская

Техрсд А. Камышпикова

Редактор А. Батыгпи

Корректор В. Брыксина

Типография, пр. Сапунова, 2

Заказ 2780/17 Изд. Хе 925 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва. 5К-35, Раушская наб., д. 4/5