Цифровой спектральный анализатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИ-Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii)4324O6

Союз Советских

Социалистических

Реслублик (61) Зависимос от авт. сви,.стельст — :;. (I =:1) . 1. Кл. 6 01г 23г00

6 (iGI ) -/36 (22) За явлено 22.11.7 l; 21) 1716348, 18-24 с присоединением заявки, (32) Приоритет—

Опубликовано !5.06.74. Бюллетень .4 22

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681 3(088 8)

Дата оиубликоьаиия описания 22.07.. 5 (») Авторы изобретепия

Э. А. Саакян, Г. Я. Бахчиев и П. И. Погребецкий (71) Заявитель Тбилисский филиал Всесоюзного научно-исследовательского института метрологии им. Д. И. Менделеева (54) ЦИФРОВОЙ СПЕКТРАЛЬНЫЙ АНАЛИЗАТОР

Изобретение относится к технике статических измерений параметров случайных процессов. Анализатор предназначен для измерения оценки спсктральной плотности мощности. 5

Известные спектральные анализаторы косвенного типа, содержащие коррелятор, генератор гармонических колебаний, устройство умножения, интегратор и устройство у.иравления, сложны и недостаточно надежны.

В предлагаемом цифровом спектральном анализаторе упрощение конструкции и увеличение надежности достигается тем, что блок памяти значений корреляционной функции соединен входами с информационными входами анализатора, а входами опроса с выходами разрядных элементов «И», первые входы которых подключены к младшим разрядам регистра сдвига. Выходы блока памяти значений корреляционной функции подключены к входам цифрового генератора гармонических колебаний, состоящего из последовательно соединенных блока элементов

«ИЛИ» и двух сумматоров. Причем первый сумматор соединен с вторым в прямом коде с соответствующим коэффициентом, а второй сумматор через блок элементов «ИЛИ» соединен с первым сумматором в обратном коде с тем жс коэффицентом передачи. Входы опроса сумматоров и вторые входы разрядных элементов «II», подключенных к входу делителя частоты, соединенного выходом с шги1ой сдвига регистра сдвига, через соответствующие элементы «И», первые входы которых подключены и отдельным входам управления анализатора, соединены с инверсным BLlxoдом старшего разряда регистра сдвига.

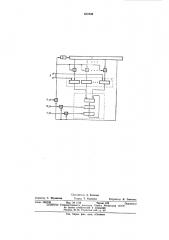

На чертеже показана блок-схема предлагаемого анализатора.

Анализатор содержит цифровой коррелятор с блоком 1 памяти значений корреляционной функции. состоящим из и (ггг+ 1) разрядных накопителей; блок 2 элементов «ИЛИ», сумматоры 8 и 4, разрядные элементы «И»

5, делитель 6 частоты, регистр 7 сдвига, информационные входы 8, входы 9, 10 и 11 управ ения и элементы «И» 12, 18 и 14, (ггг+1) -ыс и (zzz+!+1) -ые разряды соответственно накопителей блока памяти корреляционной фузокции и сумматоров являются знаковыми. Выходы прямого кода накопителей блока памяти корреляционной функции совместно с выходами инверсного кода старших разрядов сумматора 4 через блок 2, состоящий из (т+ 1) -го (zz+ I ) входовых элементов

«ИЛИ», связаны с входами младших разрядов сумматора 8, а выходы прямого кода знаковых разрядов накопителей блока памяти корреляционной функции и инверсного кода знакового разряда сумматора 4 через блок 2

4о2-106 связаны с входами 1 старших и знакового разрядог, сумматора 8. Выходы прямого кода т старших разрядов сумматора 8 подключены к входам m младши p;Bp5lдов сумматора

4, а выход i ðÿìoãо кода знакового разряда 5 сумматора 8 подключен к входам старших и знакового разрядов су.5матора 4.

11ерсд началом работы спектрального анализатора в блокc 2 зафиксированы сооТВсТстгеиио лпои иьш коль! ординат корреляциои- 1О пой функции J;,. ((и — 1) Лт), ..., 1(„(Лт), К,(О) исследуемого процесса х (/), сумматоры и":ходятси и нулевом состояшш, в делителе 6 записан код числа М; =; Лта;, где К = 2, Лт -- п5аг квантования корреляционной функции, <>; -- анализируемая I pyl.OBBя частота: младший разряд регистра 7 находится B cliIиичном состоянии!. остальные разряды — з нулевом. Т;эк55м ооразом элементы «И» 12 и

14 открыты ио своим первым входам. а э.-;cмснты «И» 5, за искл50чениэ. сосди!-:еииого с первым разрядом pcrIICTpa 7, закрыты по сBîим пс1)вым входам.

Работой анализатора управляют три Iioсле toBHTc>II èoñòè тактовых импульсов t, 12з

В такте l! на вход 9 подается и".!пульс, Koторый5, lIp014 g5I элемент «И» 12 II отк1эыть5Й по первому входу -пер,вого разряда рег:!Стра 7 элемент «И» 5, производит опрос блока памяти значений корреляционной функции и перезапись числа К,.((п — 1) Лт ) через блок

2 элементов «ИЛИ» в сумматор 8 из накопигели блока памяти значений корреляционной функции, соединенного через элемент «И» 5 с м>дадш! м (первым) разрядом регистра 7.

В такте 1, на Bxo!I 10 подается импульс, которьш, иройд» элемент «И» 18, опрашивает сум l 370@ 8 и пере!5исываст О д чис 5а

4!> и — — 1< ((н 1) хт) из сумматора .3 в сумматор 4.

В такте 12 55мпульс, поданный на вход 11, пройдя элемент «И» 14, Oilpaiu«BacT сумма- 45

1 тор 4 и перси!5сывает код чи=ла — — -, 1(,,, >.

Х ((и — 1)Ат) нз сумматора 4 через блок 2элсмснтов «ИЛИ» в сумматор 8. При этом з суммат01)е 8 ф5!Кси1эуетс5! код числа >!э

Рассмотре5шый цикл работы ана,-.изато;эа

ИОвтОр>!ется бэсз II3ixicHcpIIII М; — — 1 p33, ";-ы! . цикл работы анализатора отличается от р-Iccмотрснного выше тем, что тактовый импульс

1!, производящий опрос накопителя блока памяти корреляционной функции, через элемент 12 формирует импульс иа выходе делителя б частоты, который через промежуток времени, равный длительности задержки 13 делителе частоты, по окончании действия тактового импульса t, поступает на шину «сдвиг» регистра 7 и производит сдвиг единицы из первого разряда регистра во второй. При этом элемент «И» 5, соединенный с младшим разрядом регистра 7, закрывается по первому входу и открывается соседний элемент «И» 5. !. ледующие М; циклов протекают аналогично ирсды.lyiirriil, только тактовый импульс t! проходит именно этот элемент «И» 5 п опрашивает соответствующий накопитель блока памяти корреляционной функции.

После опроса всех накопителей, т. е. через М!а цш лов работы анализатора, в (и+1)-ом разряде регистра 7 фиксируется код единицы, элементы «И» 12, 18 и 14 закрываются и работа анализатора и1эекра5цается.

При этом в сумматоре 8 фиксируется код искомой ордииаты G,.(ü,) спектральной плотности мощности, процесса Х(Ц.

В случае оирсделсш5я взаимной спектральной плотности мощности двух процессов в сумматоре 8 ф: ксируется код действительной части, а в сумматоре 4 — код мнимой части ординаты..

Предмет изобретения

Цифровой спектральный анализатор, содержащий блок памяти значений корреляционной функц5ш, соединенный входами с HHформационными входами анализатора, а входами опроса с выходами разрядных элементов «И», первые входы которы. . подключены к младшим разрядам регистра сдвига, ornIIча50и1ийся тем, что, с целью его упрощения, оН содержит последовательно соедпненныс блок элементов «ИЛИ» и два сумматора, причем выходы второго сумматора соединены с отдельной группой входов блока элементов

«ИЛИ», другис входы .<îòîðîãî подключены к соответствующим выходам олока памяти значений корреляционной функции, а входы опроса сумматоров и вторыс входы разрядных элементов «И», подключенных к входу делителя частоты, соединенного выходом с шиной сдвига регистра сдвига, через соответствующие элементы «И», первые входы которых подключены к отдсльн!.5>! Входам управления анализ iTopB, соединены с инверсным выходом старшего разряда регистра сдвига.

432406

Составитель А. Киселев

Техред Т. Курилко

Редактор Т. Юрчиковв

Корректор И. Симкина

Тип. Харьк. фил. пред. «Патент

Заказ 259/?48 Изд. № !7!3 Тираж б?8 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5