Устройство синхронизации импульсов

Иллюстрации

Показать всеРеферат

ОПИCАНИЕ (»)434581

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 21.02.72 (21) 1750359/26-9 (51) М. 1 л. H 03k 5/00

Н 04п 5(04 с присоединением заявки Ма

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (32) Приоритет

Опубликовано 30.06.74. Бюллетень Ъ< 24

Дата опубликования описания 21.11.74 (53) УДК 621.373.43 (088.8) (72) Авторы изобретения (71) Заявитель

В. Г. Чибисов и О. Г. Светников

Особое конструкторское бюро вычислительной техники

Рязанского радиотехнического института (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

Изобретение относится к области импульсной техники и автоматики и может использоваться в устройствах преобразования, обработки и передачи информации.

Известно устройство синхронизации импульсов, содержащее триггер, логическую схему

«ИЛИ», схему совпадений и два логических элемента «И вЂ” НЕ», у которых выходы одного соединены с входами другого и с одним из входов схемы совпадений, а выход триггера соединен с одним из входов логической схемы «ИЛИ».

Это устройство синхронизации имеет низкую чувствительность.

Цель изобретения — повышение чувствительности устройства.

Для этого в предлагаемом устройстве второй вход логической схемы «ИЛИ» соединен с одним из входов триггера и выходом схемы совпадений.

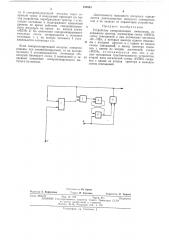

На чертеже приведена функциональная схема предлагаемого устройства.

Оно содержит триггер 1, логическую схему

«ИЛИ» 2, схему 3 совпадений и два логических элемента «И вЂ” НЕ» 4 и 5. Синхронизирующие и синхронизируемые импульсы подаются на клеммы 6 и 7. Выходы логического элемента 4 соединены с входами логического элемента 5, а выходы логического элемента 5 соединены с входами логического элемента 4. Выходы логического элемента 5 соединены с одним из входов схемы 3 совпадений. Второй вход логической схемы «ИЛИ»

2 соединен с одним из входов триггера 1 и выходом схемы 3 совпадений.

Устройство работает следующим образом.

В исходном состоянии триггер 1 находится в состоянии «О». Нулевой потенциал с выхода триггера 1 поступает на один из входов схемы «ИЛИ» 2.

При отсутствии синхронизирующего импульса на клемме 6 с выхода элемента 5 снимается потенциал «1», поступающий на вход схемы 3 совпадений и элемента 4. На выходе схемы 3 и на выходе устройства появляется потенциал «О», который поступает на установочный вход триггера 1 и один из входов схе20 мы «ИЛИ» 2. Таким образом, в исходном состоянии с выхода элемента 4 снимается потенциал «1».

Синхронизируемый импульс, поступающий

25 на клемму 7, опрокидывает триггер 1. Потенциал «1» с выхода триггера 1 через схему

«ИЛИ» 2 поступает на вход элемента 4 и устанавливает его в положение, при котором на его выходе потенциал «О», который запи30 рает элемент 5. Поступающий затем на клем434581

Составитель 10. Еркин

Техред Н. Куклина

Корректор О. Т орина

Редактор Е. Караулова

Заказ 8016/15 Изд. 11о 1201 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 му 6 синхронизирующий импульс чсрсз открытую схему 3 совпадений проходит на выход устройства, перебрасывает триггер 1 в исходное состояние и поддерживает единичный уровень во время действия синхронизирующего импульса на одном из входов схемы

«ИЛИ» 2. По окончании синхронизирующего импульса схема возвращается в исходное состояние, т. е. на выходе элемента 4 устанавливается потенциал «1».

Если синхронизирующий импульс появится раньше, чем синхронизируемый, то на выходе элемента 5 устанавливается потенциал «0», который блокирует схему 3 совпадений и запрещает появление синхронизирующего импульса на выходе.

Длительность выходного импульса определяется длительностью импульса синхронизации и не зависит от параметров устройства.

Предмет изобретения

Устройство синхронизации импульсов, содержащее триггер, логическую схему «ИЛИ», схему совпадений и два логических элемента

«И — НЕ», у которых выходы одного соедине1О ны с входами другого и с одним из входов схемы совпадений, а выход триггера соединен с одним из входов логической схемы

«ИЛИ», отличающееся тем, что, с целью повышения чувствительности устройства, 15 второй вход логической схемы «ИЛИ» соединен с одним из входов триггера и выходом схемы совпадений.